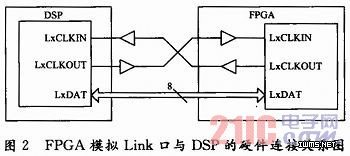

Link协议通过8位并行数据总线完成双向数据传输,与数据总线配合的还有相应的时钟信号线LxCLKIN,LxCLKOUT。

2.1 Linkport口的传输协议

Linkport口传输数据时,每8个周期传送一个4字组(16 B),在时钟的上升沿和下降沿均传送一个字节。在传送过程中,发送端将检测接收端的LxCLKOUT信号,仅当接收端将它的LxCLKOUT置为高时,即接收端处于接收方式,且有空闲的缓冲时,发送端才可以启动下一个传送过程。

传送启动过程如图3所示,发送端驱动信号LxCLKOUT为低电平,以此向接收端发出令牌请求,发出令牌请求后,发送端等待6个周期,并验证LxCLKIN是否依旧为高,若是则启动传送过程。传送过程启动一个周期以后,接收端将发送端的LxCLKIN驱动为低,以此作为连接测试。若接收完当前4字组后接收端无法再接收另外的4字组,则接收端保持LxCLKIN为低。这种情况下,缓冲空闲后LxCLKIN信号被禁止。若缓冲为空,则接收端将置LxCLKIN为高电平。

作为同步信号,LxCLKOUT信号由发送端驱动。数据在LxCLKOUT的上升沿和下降沿处锁存到接收缓冲中,发送和接收缓冲都是128b宽。 LxCLKIN信号由接收端驱动,发往发送端,它通常用作“等待”指示信号,但LxCLKIN信号也可以用作连接测试信号,保证接收端能正确地接收当前传送数据。

当LxCLKIN信号用于等待指示信号时,接收端驱动LxCLKIN信号为低电平。若LxCLKIN信号保持低电平状态,则发送端可以[完成当前的4字组传送,但无法启动下一个垂字组传送。若还有其余的数据需要传送,发送端需将LxCLKOUT置低,并等待接收端将LxCLKIN驱动为高电平。如果在第12个时钟沿到来之前LxCLKIN变为高电平,则紧跟着传送的将是新的4字组。