摘要:系统采用CY7C68013及其配置芯片EEPROM完成USB接口部分的功能,采甩ACT8990完成边界扫描部分的功能,为完成部分逻辑功能及对此控制器设计的部分电路加密,采用CPLD EPM3032A实现。接着,给出了整个控制器的软件设计方案,具体讨论了CY7C68013的固件设计,以及利用WindowsDDK开发包开发固件装载驱动程序及控制器驱动程序的方法。调试结果表明,研制的边界扫描控制器功能正常,符合设计要求,具有即插即用、无需外部供电、连接简单可靠等优点。

关键词:边界扫描;USB2.0;JTAG;WDM驱动程序

0 引言

随着超大规模集成电路(VLSI)、表面安装器件(SMD)、多层印制电路板(MPCB)等技术的发展,使得统一测控系统综合基带印制电路板上电路节点的物理可访问性正逐步恶化,电路和系统的可测试性急剧下降,常规测试面临挑战。通过研究VLSI芯片资料表明,大多数VLSI芯片都带边界扫描结构,如果将边界扫描技术应用到板级测试中,无疑将对电路板的连接故障和器件失效的准确诊断起到非常重要的作用。边界扫描测试主控系统是实现这一技术必不可少的硬件系统。从JTAG(Joint Test Action Group)提出该技术至今的十几年中,边界扫描测试技术已得到了一些应用,并将有广阔的应用前景。本设计在分析边界扫描测试受控系统工作机制的基础上提出一种基于USB总线的边界扫描测试主控系统的设计方案和实现电路。此方案具有结构简单、成本低、便携性的特点。

1 边界扫描结构及基本原理

1.1 边界扫描技术的基本原理

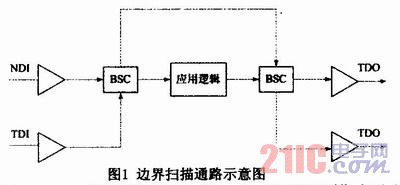

边界扫描技术的主要思想是通过在芯片管脚和芯片内部逻辑电路之间增加由移位寄存器构成的边界扫描单元,实现对芯片管脚状态的串行设定和读取,使管脚具有可控性和可观测性。由于移位寄存器允许测试数据移位、更新溯试和捕获锁存,因此它不仅可以用来测试单独的一个芯片,而且可以对电路板进行互连测试。图1给出了边界扫描通路示意图。其中,边界扫描单元在主IC的测试数据输入端(TDI)和测试数据输出端(TDO)之间形成了一个扫描通道,当IC处于正常工作状态时,输入输出信号自由通过边界扫描单元,从正常数据输入端(NDI)到正常数据输出端(TDO)。图1边界扫描通路示意图

1.2 边界扫描物理结构

边界扫描测试的基础是边界扫描测试总线和设计在器件内的边界扫描结构,边界扫描测试总线由TDI(测试数据输入)、TDO(测试数据输出)、TMS(测试模式选择)、TCK(测试时钟)、TRST(测试复位)5条线构成,主要完成测试向量输入、测试响应向量输出和测试控制功能。器件内边界扫描结构主要由TAP测试存取口、TAP控制器和必需的寄存器组成。TAP控制器接受来自边界扫描测试总线的命令,控制边界扫描单元的行动,实现对器件管脚状态的设定、读取和隔离。

1.2.1 寄存器

JTAG边界扫描寄存器至少应包括边界扫描寄存器(DR)、指令寄存器(IR)和旁路寄存器。

(1) 边界扫描寄存器。边界扫描寄存器用于存放测试数据和测试响应数据,它由串行移位级和并行锁存级组成。边界扫描寄存器的工作方式为:加载到TDI的测试数据在TCK的上升沿串行移人边界扫描寄存器,寄存器原来内容在TCK的下降沿被串行移出到TDO,移入移位寄存器的数据可以被锁存到并行输出锁存器中;对应于输出引脚的并行锁存器可并行输出到器件的引脚,移位寄存器可以并行捕获到器件的逻辑输出;对应于输入引脚的并行锁存器可以并行输出到器件的内部逻辑,移位寄存器可捕获输入引脚信息。

(2) 指令寄存器。指令寄存器由串行移位级和并行锁存级组成,其位数由芯片生产厂家定义。常用的指令包括EXTEST、BYPASS、SAMPL-E、INTEST等。TAP控制器根据指令寄存器中选择的指令不同选择将指定的寄存器连接到TDI和TDO之间。

(3) 旁路寄存器。旁路寄存器由一位移位寄存器组成,当其被选通时,直接连接到器件的TDI和TDO之间从而获得最短的扫描路径。旁路寄存器的主要作用有:a.当集成电路IC不需要数据寄存器的扫描存取时将其从扫描链上脱离从而缩短边界扫描结构的扫描通路长度;b.在测试期间,使集成电路IC脱离某种工作模式。