3.2 EZ-USB FX2时序设计

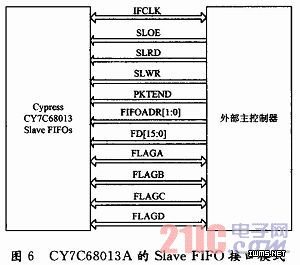

在本设计的FPGA中,设计了如图6的外部主控制器的功能逻辑。由于DSP端Linkport口数据传输速率很高,而在USB端的速率可能无法跟Linkport口的数据率相匹配,故在FPGA中开辟一个2KB的FIFO,经由Linkport上传的数据首先传送到FIFO中,之后再经由USB口上传至主机。为了保证数据传输的完整性,设计USB的数据传输速率为DSP Link口的1/8。在此,对FPGA逻辑应用Modelsim软件进行了仿真,仿真结果如图7所示。

图7中,在LxCLKIN时钟的上升沿和下降沿将DSP_Data中的数据写入到FPGA的FIFO中,然后再把FIFO中的数据从数据线USB_Data中输出给EZ-USB FX2的FD数据线,最后经由USB传送给主机。图中USB_Data的数据率明显只有DSP_Data数据率的1/8,是符合设计要求的。

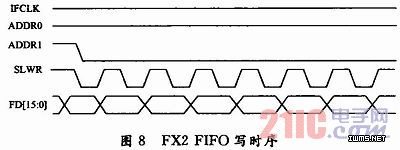

在上传传输时,采用异步自动输入方式。EZ-USB FX2芯片FIFO异步写时序如图8所示。根据此时序,在本设计中,FPGA输出的USB_Data信号提供给USB的FD数据线,FPGA输出的USB_SLWR提供给USB的SLWR,USB端便能在SLWR的下降沿把数据线FD中的数据写入到FX2芯片FIFO中,并由USB传送给主机。

4 结语

本文重点对DSP扩展USB接口的数据上行通道的硬件设计进行了详细论述。本系统经测试验证,通过该扩展USB接口,配合定制的上位机软件,DSP数据上传PC机的速率平均达到8 MB/s以上,连接可靠稳定,满足对DSP变量实时监测的数据率需求,同时可通过此接口完成程序的加载与烧写功能。仅需一台带USB接口的PC机,就能完成弹载DSP系统的实时测试与在线程序加载,简捷、通用、方便,具有显著的工程实用价值。