・上一文章:基于IOCP的远程屏幕监控系统

・下一文章:新型蓄电池充电方案解决充电失衡

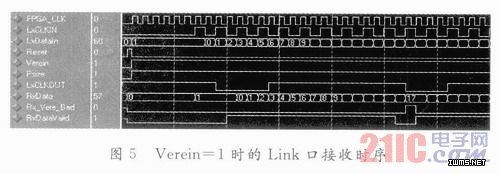

图5是FPGA内实现DSP数据上行的Linkport口接收时序仿真图(基于Modelsim仿真软件)。

Link口协议的一大特点就是在收发数据时可以选择是否需要校验位VERE比特,VERE的启用或关闭可以通过ADSP-TS101中的寄存器来设置,也可以通过FPGA模块中的Verein信号置高或置低来设置。该设计在FPGA中设置VERE信号的启用或关闭。当VERE启用后,FPGA模块中的输出信号Rx_Vere_Bad用于表征最后接收的128 b数据是否正确。由于使用VERE有两个好处,一是能保证数据的完整性;二是能减小在两个时钟不严格一致的系统中传输数据时产生数据重叠的可能性。因而在设计中采用了带数据校验的传输方式。