使用高速ADC(模数转换器)进行产品开发时,或者评估这些器件以便用于设计时,必须注意ADC的输出谐波。ADC通常使用差分输入,使共模噪声和失真降至最低,但只有在平衡和对称的情况下,这些输入才能发挥最大效用。可以使用一个由两个RF信号发生器和一个振荡器组成的测试系统,来测量差分不平衡对ADC输入的影响。

当ADC的差分模拟输入由于驱动错相而变得不平衡时,器件输出中的偶次阶失真会提高。下面说明如何测量高速ADC的谐波性能,以便了解差分不平衡的影响。

1 测试设置

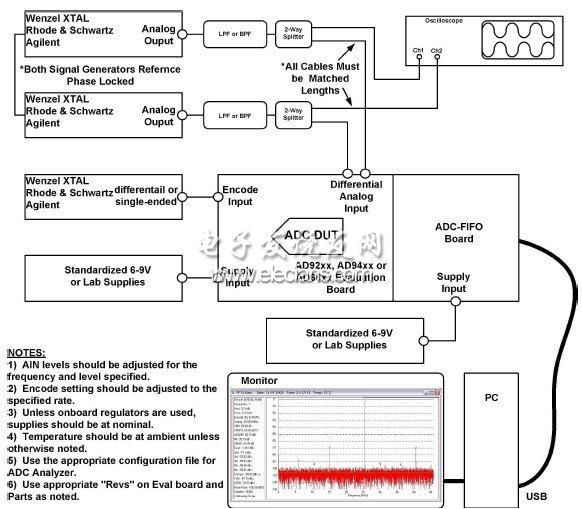

测试设置(如图1所示)使用两个RF信号发生器驱动2 MHz至300 MHz频率范围的ADC模拟输入。必须使信号发生器的参考频率彼此锁定,这样有助于限制相位随时间变化而发生的非预期漂移。每个信号发生器的输出均通过一个低通滤波器,低通滤波器连接到一个双路低损耗分路器,从而可以利用示波器来观察差分信号。各输入端应使用相同制造商和型号的低损耗分路器。为了使用ADC,需要一个评估板。此外,分路器前应使用两个相同制造商和型号的低通滤波器或带通滤波器,以便限制来自信号发生器的宽带噪声。

图1 用于测量相位不平衡的测试设置

一致的模拟信号路径可以将测量误差降至最小。分路器前后的电缆应为同一类型并且长度相同。从信号发生器到分路器的电缆长度必须相同,这点很容易明白。分路器之后的电缆长度(连接到ADC和示波器)容易忽略,也需要相同的长度以保护测量结果。如果评估板上具有从连接点到ADC引脚的走线,则从分路器到示波器也必须复制相同长度的走线。因此,考虑到走线差异,从分路器到示波器的电缆长度可能需要略有不同。同等信号路径可确保您在示波器上查看的信号能够准确代表ADC模拟输入引脚上的信号。

推荐方法似乎应当是把示波器探头引线直接焊接到ADC的模拟输入端,以便获得正确的长度匹配,但这种方法会增加ADC探测模拟输入端的寄生电容和电感,引起测量波动。适当的探头结合电缆和分路器,可以将寄生电容和电感降至最低,从而在示波器上产生更干净的信号。

务必使用适当带宽的示波器,以便显示差分模拟输入测试频率。注意随时监控各信号发生器,测试信号应保持稳定。可以使用示波器的数学功能来确保两个信号具有正确的相位和幅度关系,即当差分输入180°反相时,信号A + 信号B应尽可能接近0 V。当然,随着信号偏离180°,信号幅度之和应增大,但无论相位如何偏移,都应当能够使用该信号。由此便可确定正确的相位参考点(180°反相),从该点开始测试。

评估板需要一个干净的时钟信号。务必使用低相位噪声的振荡器或信号源,这样才不会限制ADC的性能。ADI公司使用250 MHz Wenzel晶振和TTE 250 MHz带通滤波器。图2从左至右分别显示的是示波器、滤波器和高速ADC评估板。

图2 由示波器、低通滤波器和ADC评估板(从左至右) 组成的采样时钟设置

当ADC的模拟输入与示波器不同相时,两个信号之间的差分幅度不匹配会导致ADC输入信号的基频功率略有降低。应使用FFT(快速傅里叶变换)监控测试频率在所有相位变化下的基频电平。对幅度进行微调,确保ADC始终以相同的电平工作。基频功率的差异会导致结果不准确,说明ADC由于相位和基频功率变得不准确而表现不佳。

图3显示同一器件以相同频率工作,并使用ADI公司Visual Analog软件获得的两个FFT读数。图3a和图3b分别突出显示了当两个输入信号之间的相位差为0°(图3a)和20°(图3b)时的基频幅度差异,图3b中的二次谐波功率有所提高。

图3 a) 当两个输入信号之间的相位差偏移20° (b)时, 二次谐波(标记为“2”)的功率提高