・上一文章:太仓牌KC-28D窗式空调机原理图

・下一文章:太仓牌LFD-6立柜分体式空调机原理图

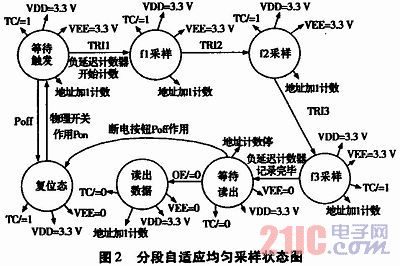

在存储测试开始之前,通过软件编程将采集存储过程分为几个阶段,根据被测信号的变化,每一个阶段的采样频率、存储点数、采样开始时间会作自适应的调整。首先接通电源使电路处于复位态,此时数字电源VDD为通电、模拟电源VEE为断电状态,系统中只有FPGA控制模块工作;然后对电路编程设定各个环境的采样频率,给电路上电,电路进入等待触发态,此时VDD、VEE通电,存储器、AD转换器启动,开始采样,地址计数器开始工作;触发信号TRI1到来后,进入f1采样态,系统按编程设定的采样频率f1开始采样,负延迟计数器开始工作;2环境触发后,系统按照设定的采样频率f2进行采样,此时处于f2采样态;3环境触发后,系统按采样频率f3采样,处于f3采样态;当负延迟计数器计满设定值时,地址计数器和负延迟计数器均停止工作,VEE断电,系统进入等待读出态;在读出数据态,地址同步推进,直到读完所有的数据。

2.2 变频采样的模块设计

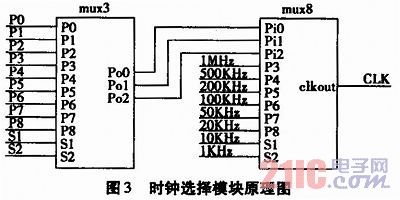

采样频率决定了采样信号的质量和数量,采样频率太高,会使采得的信号数量剧增,占用大量的存储单元,采样频率太低的话,会使模拟信号的某些信息丢失,恢复出的信号会出现失真。为了达到最佳效果,必须根据信号的特点选择合适的采样频率。图3为设计的采样时钟选择模块。