设计可选采样频率有八种,如图3中1 MHz~1 kHz,都是由FPGA的时钟模块分频而来,可根据实际情况修改。S1、S2为环境选择信号;P0~P2、P3~P5、P6~P8三组信号分别是三个环境的采样频率控制字,在测试前根据环境采样频率的需要来编程设定;模块mux8为8选1数据选择器,根据输入的三个控制字来选择对应的采样频率输出。系统上电后,环境选择信号S1、S2为“00”,模块mux3将1环境的采样频率控制字P0、P1、P2输入到模块mux8中,系统自动以1环境的采样频率进行采样;2环境的触发信号到来时,S1、S2由“00”跳变为“10”,2环境的采样频率控制字P3~P5送到mux8中,以2环境的采样频率进行采样;当3环境的触发信号来临,S1、S2由“10”跳变为“11”,3环境的采样频率控制字P6~P8被选中,系统以3环境的采样频率采样。

3 实验验证

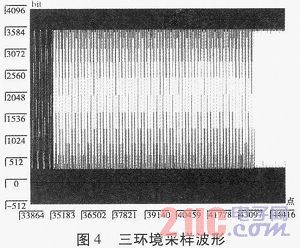

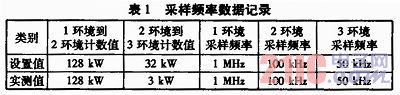

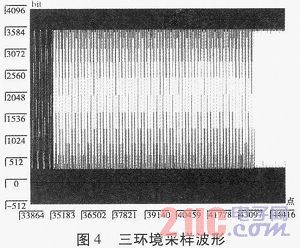

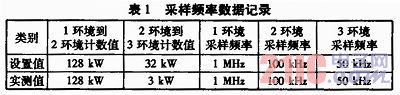

该实验对标准信号发生器输出的正弦波信号进行采集和存储,采样策略选择为三环境采样,1环境采样频率为1 MHz,2环境为100 kHz,3环境为50 kHz,外触发进入1环境,计数触发进入2环境,计数值128 kW,计数触发进入3环境,计数值32 kW。系统采样完毕后,连接到计算机通过上位机软件读取数据,实验波形如图4。

设置为计数128 kW进入2环境,计数32 kW进入3环境,而系统负延迟为8 kW,分为4个通道,因此1、2环境的分界点为(128+8)·1024/4=34816点,2、3环境的分界点为(128+8+32)*1024/4=43008点,实验波形与计算值相符。如表1所示:

通过上表可以看出,系统变频采样模块的设计满足系统的要求,并且系统是完全按照设定的采样策略进行采样的。

4 结束语

介绍了一种用FPGA实现的动态测试存储测试系统。通过实验验证,表明系统能对信号进行不失真采样存储。证实了所设计的采样策略对多种变化规律的信号采集具有通用性,实现了对信号的变频采样,扩展了系统的应用范围。

上一页 [1] [2] [3]