摘要:为了在提高数据采集卡的速度的同时降低成本,设计了一种应用流水线存储技术的数据采集系统。该系统应用软件与硬件相结合的方式来控制实现,通过MAX1308模数转换器完成ADC的转化过程,采用多片Nandflash流水线数据存储模式对高速采集的数据进行存储。搭建硬件电路,并在FPGA内部通过编写VHDL语言实现了采集模块、控制与存储模块和Nandflash存储功能。调试结果表明,芯片的读写时序信号对应的位置准确无误,没有出现时序混乱,且采集速度能保持在10 Mh/s以上。系统实现了低成本、高速多路采集的设计要求。

关键词:高速采集;流水线存储;FPGA

引言

为使计算机能对数据采集系统输入的模拟量进行处理,必须经由数据采集系统将模拟量转化为数字量。FPGA是在CPLD等逻辑器件的基础上发展起来的,其高集成度能大大缩小电路板的尺寸,降低系统成本,提高系统的性能和可靠性,适合于时序、组合等逻辑电路的应用场合。一个完整成型的探测系统通常都有采集储存部分,无论是电信号、光信号、声音信号等在被探测器接收到后,大部分都需要转化为数字信号才能再传给处理器完成分析、判断的过程。现在的一些高速大容量采集系统,往往价格比较昂贵。本论文主要论述一种应用FPGA等来控制,采用多片Nandflash存储的低成本、高速、多路、可靠的数据采集系统,本文主要探讨硬件设计和存储设计。

1 系统总体设计方案

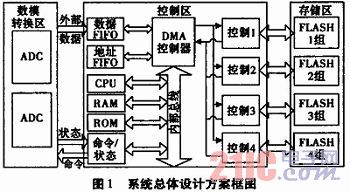

数据采集系统的工作原理是:各种信息经过传感器后转化成模拟电量信号,通过ADC将模拟量转换为数字量信号,而后进行传输存储和处理。本系统中,在软件和硬件相结合的控制下,系统将采集到的模拟信号经过A/D转换器件转换后,将转换结果先缓存到FIFO,再转存到非易失性Nandtlash阵列中。其中,FIFO不但可以实现缓存功能,还可以解决A/D转换之后数据位数跟Nandflash存储器的数据线位数不匹配的矛盾。如图1系统总体设计方案框图所示,本系统采用FPGA内部软核mICroblaze处理器作主控制器即软件控制器,而FPGA内部逻辑资源则用于产生硬件控制时序,整个系统就是在两者相结合协调下进行数据的采集以及传输。