・上一文章:基于TMS320F2812和ADS8364的智能节点设计

・下一文章:一种基于CPLD的超声波测厚系统的设计

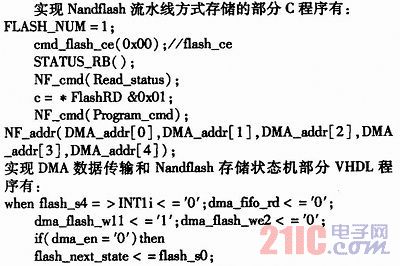

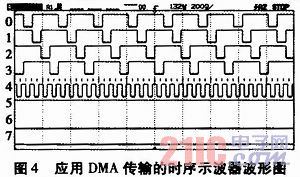

在数据加载期间本系统应用DMA传输控制方式,即:每当FIFO的半满标志信号HF产生一次有效的电平时,处理器就启动一次中断,在中断程序中,处理器将完成对Nandflash写命令和地址,以及DMA控制器的启动。一旦DMA控制器启动,处理器就将转入后台进行有效地址的运算等而不参与数据传输过程,整个数据从FIFO到NanDILash存储器的传输过程是由FPGA内部编写的DMA控制器控制完成。启动一次DMA控制器传输一页2048个字节的数据,一次中断将完成16K字节的传输。应用DMA传输的时序示波器波形图如图4所示:第0,1,2,3通道是FIFO的读数据时序波形,第4通道是Nandflash的写时序波形。一次DMA传输完成后,则处理器还要判断当前页是否为最后一页第64页,若不是最后一页第64页,则页地址加1,继续进行DMA传输采样数据操作。如果当前页为最后一页第64页,则判断当前块是否为本文件的最后一块,若不是最后块,则块地址加1,再跟无效块表对照判断此块是否为有效块,若是则页地址置0,继续进行DMA传输采样数据操作;若当前块已是本文件的最后一块,则本文件的采集数据操作完成即本次采集完成。

4 结论

试验结果表明,采集系统性能稳定,采集速度能保持在10 Mb/s以上,符合设计要求。该系统对选用低成本、高速、可靠性采集的硬件设计具有实用价值。