2 硬件控制器的设计

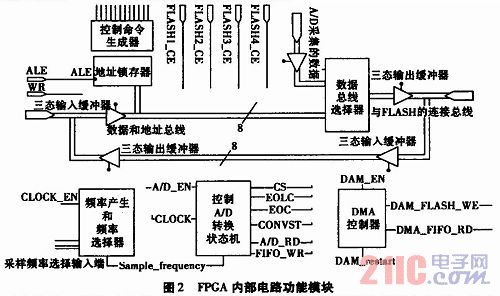

整个数据采集系统含有数据采集模块和数据传输模块。其中数据采集模块由AD数据转换模块和Nandflash数据存储模块组成。系统采用USB接口做数据传输模块,在此不作为本论文的重点进行描述。在数据传输部分本系统采用了DMA传输技术。其FPGA内部电路功能模块如图2所示。

其中ALE,WR分别连接处理器的地址锁存和WR引脚。而处理器设置成地址总线和数据总线分时复用的模式。这样FPGA可以通过ALE信号来锁存处理器的地址。而控制命令生成器用来译码产生相应的命令和操作。DMA控制器是我们自己编写的特定的控制器,它需在收到处理器的DMA使能命令的情况下使得DMA_EN有效,然后在收到DMA开启信号DMA_restart后,才会启动一次DMA传输数据,每启动一次传输一页2 K的数据。在传输过程中,因为是多片FIFO的读,为了数据不会乱,我们通过一个特定的控制器将DMA_FLASH_WE和多片FIFO的DMA_FIFO_RD匹配的统一起来产生了多片FIFO轮换读的操作。

在采样速率选择的设计中,我们是应用先微处理器的软件系统给FPGA的硬件系统一个采样速率选择值,而后FPGA的硬件系统内部将译码微处理器给的频率值,频率选择器将根据这个数值产生相应的频率输出,频率选择器输出的频率又将输入到控制AD转换的状态机里,这样控制AD转换的状态机将根据输入的频率进行相应的频率采集、数据的读取和向FIFO写数据等操作。

3 控制与存储模块

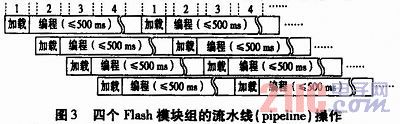

本系统在存储方式设计时采用流水线操作方式。Nandflash存储器的写入有两个阶段:数据加载阶段(即通过I/O端口将数据写入页数据寄存器)和编程阶段(在芯片内部,将页数据寄存器中的数据转存到非易失性存储单元内)。数据编程阶段是自动进行的,不需要外部系统的其它操作,但它需要很长的时间,其典型值是200μs。而如果采用流水线存储方式就可克服Nandflash芯片写入速度较慢的缺点。应用流水线操作方式对Nandflash存储器进行写操作流程原理如图3所示。首先对第一片Nandflash进行数据的加载,数据加载完后,第一片Nandflash随后就将进入自动数据编程阶段;然后再对第二片Nandflash进行数据的加载,数据加载完后,第二片Nandflash也将进入自动数据编程阶段;然后依次对第三片Nandflash和第四片Nandflash进行相同的上述操作。而当第四片Nandflash数据加载完后,第一片Nandflash刚好已经自动编程数据结束,接着再从第一片Nandflash重复刚开始的加载数据和自动编程数据阶段。就这样如此循环一直到数据采集完成。这就是流水线的存储方式。从整体时间来看,整个系统在一直的进行着数据的传输和存储。