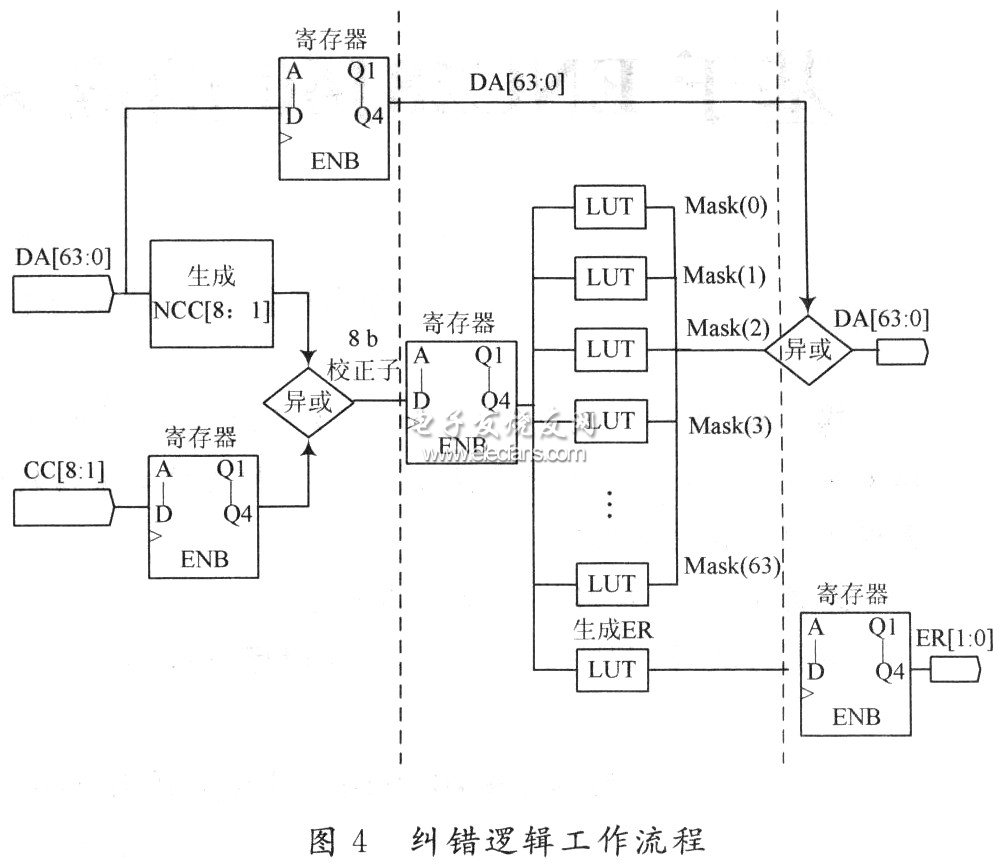

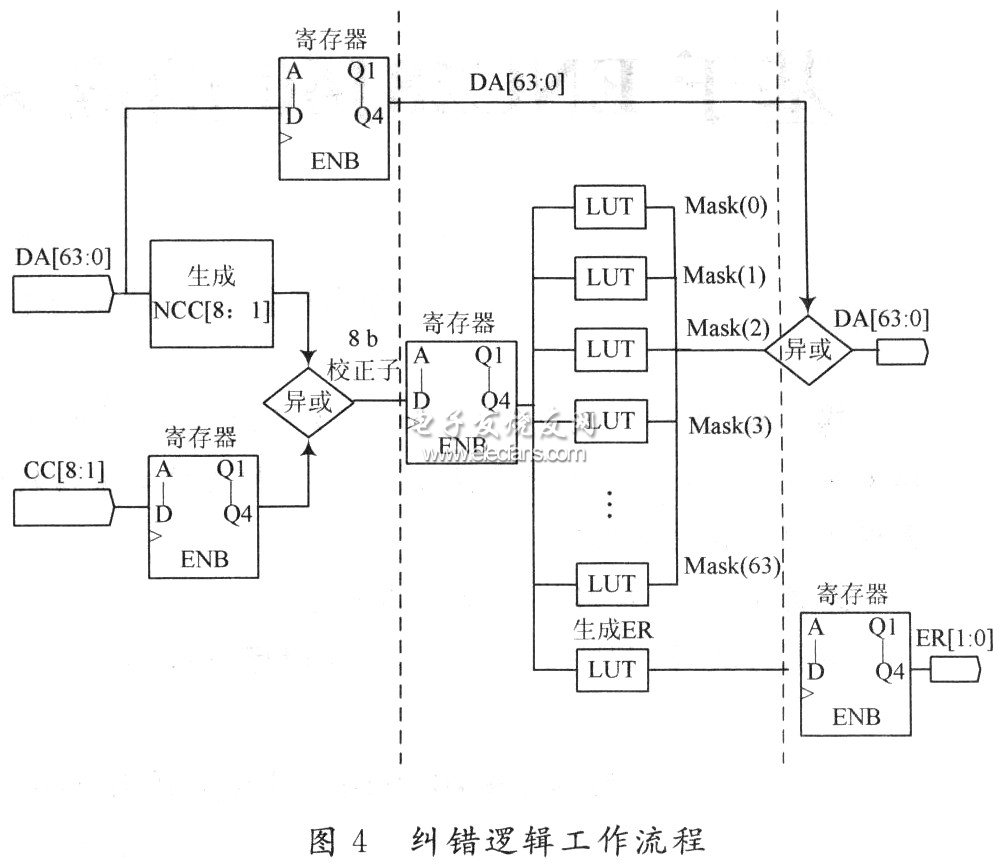

FPGA的检纠错逻辑设计采用VHDL语言实现。设计使主存储器SRAMl中的64位数据新生成的NCC[7:0]与SRAM2中的7位校验位CC[7:0]一起经过异或运算,生成8位的校正子,其中前7位就对应于前述定位错误数据的行号和列号的值,第8位用于判断是否出现双位元错误。8位校验子的值可以求出1个64位纠错掩码(Mask),用以校正单位元错误。如果未检测到错误,此掩码的所有位都为零。如果检测到单位元错误,相应掩码会屏蔽除错误位之外的所有位。下一阶段,使用原始数据对此掩码进行异或运算。最终,错误位被反转(或校正)至正确状态。如果检测到双位元错误,所有掩码位也都为零。使用1个双位的数组(ER[1,O])用于报告检测的错误类型(“OO”表示无错、“01”表示单位元错误、“10”表示双位错误、“11”表示无法判断的多位错误)。整个纠错逻辑的工作过程如图4所示。生成错误类型报告数组和相应的校正掩码的工作都在同一时钟周期内完成,体现了采用FPGA进行并行处理的独特优势。

3 结 语

对综合后进行仿真的结果进行分析,期间人为地加入1位、2位、3位随机分布的数据位错误,该系统能够在2个系统时钟周期内对1位错误的情况成功地检测并予以纠正;对2位和3位错误情况也都进行了正确的类别判定。仿真结果表明,设计的系统比较理想,能满足设计要求。

上一页 [1] [2] [3]