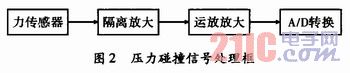

力传感器采样数据送两级运放LM324进行调节放大后,送入双12位A/D转换器的VA1和VA2。AD7862以250 kHz的采样率同时进行4个通道信号采样,输入给片内采样一保持放大器的信号经差分并在ADC输入期间内保持,将模拟信号转换成系统需要的数字信号。

1.1.2 GSM、GPS模块

控制中心GSM Modem选用Siemens公司的无线通信引擎TC35终端,它由引擎模块、天线及其外围电路组成。监控终端TC35i模块的用户口采用40脚的ZIP插座,其中包含了模拟音频、RS232接口、SIM卡接口和电源,外围电路主要是SIM卡电路和启动控制电路。

GPS数据采集模块采用美国泰雷兹导航定位公司(Thales Navigation)的一款高性能、低功耗的小型GPS接收机B12 OEM,通过独特的软件算法和最新的GPS技术,泰勒兹公司把B12优化成快速处理、导航、车辆跟踪、移动数据、远程信息处理的手持产品。它支持差分远程操作,可提高系统差分定位精度。

1.2 片内逻辑的设计

将概念结构转化为与实际系统相应的数据模型的过程称为逻辑结构设计。FPGA的片内逻辑设计,包括系统模块和用户自定制逻辑区域。系统模块是指由SOPC builder自动生成的设计,SOPC builder会根据用户选择的IP生成相应的HDL描述文件。用户自定制逻辑区域内可以包含用户自定义的Avalon外设,以及与系统模块无关的其他用户自定制逻辑。

利用FPGA中的可编程逻辑资源和现有IP软核,如Nios II核、片内Boot ROM、用于FIFO的片内双口RAM、定时器Timer、JTAG UART等来构成该嵌入式系统处理器的接口功能模块。

1.2.1 串行通信接口UART

UART是基于RS232通信协议的串行通信接口,用于在ALTEra的FPGA中实现简单的RS232异步发送和接收逻辑。因为GSM、GPS模块两者的数据通信接口都为标准RS232串行接口,因此,可方便地与NiosⅡ系统的串口相连。

图1所示的监控终端硬件设计框图中,UART-1连接GSM短消息发送模块TC35i,利用AT命令控制TC35i收发信息和拨号,控制中通过RS232串口与GSM TC35 Modem通信。GSM模块接入GSM网络,按照规定的通信协议,以短信方式完成航标的工作参数与状态信息的传输。

UART-2连接GPS OEM板,通过GPS定位模块的接收天线接收导航信号,经接收机解调处理,获取航标灯的位置信息,包括航标灯的代码、位置的经纬度、测定时间等信息,再将经纬度坐标通过无线通讯系统传送给监控中心。