简介:为了在USB 3.0中实现数据的8 b/10 b编解码,采用了查找表法和组合逻辑相结合的方法,把8b/10b编解码分解成5 b/6 b编解码和3 b/4 b编解码,用Verilog HDL语言实现了算法的描述,并通过了Modelsim仿真,然后在FPGA上实现了具体的硬件电路。采用500 MHz的时钟信号,经过测验满足了USB 3.0的传输速率5 Gb/s。该创新方法使用了少量逻辑,实现了8 b/10 b编解码器,并且满足USB 3.0高速数据传输的要求。

关键词:USB 3.0;8 b/10 b编解码;RTL设计;仿真验证

引言

8 b/10 b是目前许多高速串行总线采用的编码机制,如USB 3.0,1394b,Serial ATA,PCI Express,Infini-band,Fiber Channel,RapidIO等总线或网络。8 b/10 b编码方式最初由IBM公司于1983年发明并应用于ESCON(200M互连系统),发表Al Widmet和Peter Franaszek IBM刊物的“研究与开发”。8 b/10 b编解码之所以能得到广泛的运用,主要有以下优点:采用嵌入式时钟,可保持DC平衡;能够更加有效地检测错误;隔离数据码元和控制码元。

1 USB 3.0中的8 b/10 b编解码原理

在USB 3.0分层结构中,发送端先对数据或者控制字(K)加扰,然后把加扰后的8 b数据编码成10b发送出去;接收端先把接收到的10b数据进行解码得到8 b数据,然后再解扰得到原始数据。

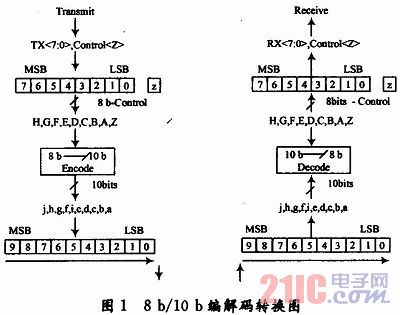

8 b/10 b编码包含对256个数据字符和12个控制字符的编码。数据字符和控制字符分别用Dx,y和Kx,y表示,其中x表示与8 b的低5位(EDCBA)对应的十进制数值;y表示与8 b的高3位(HGF)对应的十进制数值。发送端在编码时,根据编码表将低5位变成6位,高3位变成4位。编码完成后,将10 b的并行字符转换成串行发送出去。接收端在解码时先进行串并转换得到10 b字符,再将该字符分解成6 b和4 b,根据相应编码表看是否有效,最后完成解码。编解码转换流程如图1所示。

不平衡度disp(disparity)表示编码后1个码字中“1”数目与“0”的数目差。“1”用+1表示,“0”用-1表示,码字中的所有“+1”与“-1”之和就是disp。8 b/10 b编码的disp取3种状态:“+2”(6个1与4个0),“0”(5个0与5个1),“-2”(6个0与4个1)。而运行不一致RD(Running Disparity)是一个二进制参数,只有正、负2种状态,用于编码模式控制。在8 b/10 b编码表中,10 b字符分为2种码表(RD-和RD+)。编码过程中,通过对RD值正负的判断来选择对应码表,如果当前RD为负(RD-),编码器会在RD-编码表中选择对应值输出,并且检测对应输出的10 b值的disp,如果disp=0,则RD不变保持RD-,否则RD值变为RD+;如果当前RD为正(RD+),则在RD+编码表中选择对应值输出,并且检测输出值对应的disp,如果disp=0,则RD不变保持RD+,否则RD变为负RD-。总之,在disp为正或者负时,RD发生交替变换,这种方法是为了使0和1分布更均匀,减小差分信号的直流分量。