摘要:频率合成器可以提供大量精确、稳定的频率作为无线通信设备的本振信号。简要介绍了锁相环频率合成器的基本原理,并利用整数N锁相芯片ADF4112设计了一个宽波段的频率合成器。讨论了其中主要元器件的选择和环路滤波器的设计,利用先进设计系统(Advanced Design System,ADS)仿真软件对设计方案进行频城和瞬态响应仿真,并使用其中的优化工具对各个参数进行优化。仿真与优化结果验证了频率合成器的可行性,同时可以得到优化后环路滤波器的参数。

关键词:射频;频率合成器;环路滤波器;ADS仿真

在现代通信系统中,对频率源的频率稳定度和准确度的要求越来越高,只采用晶振是不能满足需要的。而频率合成技术则是利用一个或多个高稳定度的晶体振荡器产生一系列等间隔的、离散的、高稳定度的频率,可为通信设备提供大量精确且能迅速转换的载波信号和本振信号,完全满足现代通信的需要。其中锁相频率合成器具有工作频带宽、工作频率高、频谱质量好、方案简单、造价低等优点,在目前现有的频率合成方法中应用最为广泛。

1 锁相环频率合成器的基本原理

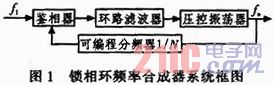

一个典型的频率合成器主要由鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)和可编程分频器组成。其系统框图如图1所示。

基本工作原理是由晶体振荡器提供参考输入信号,经分频后得到鉴相频率fi与来自VCO的输出信号fo经N分频后得到的反馈信号进行鉴相,所产生的相位误差信号,经电荷泵作用后转换为与相位误差成比例的正/负电流脉冲串,然后利用环路滤波器对来自电荷泵的电流脉冲求积分,向VCO调谐端口提供干净的电压,从而实现对VCO的频率控制。当环路锁定时,输出频率与鉴相频率的关系如下:

![]()

N分频器的分频比不同时,输出频率fo也随之变化。所以,只需要选择合适的晶体振荡器和选择合适的N值就能产生所需要的频率信号。

2 锁相频率合成器方案的设计

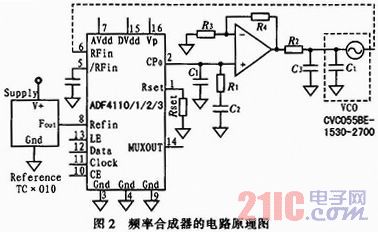

设计的频率合成器的技术指标为输出频率1580~2500MHz,频率间隔200kHz,输出杂散优于-65dBc,输出相噪优于-80dBe/Hz@1 kHz。根据技术指标来选择合适的芯片,其中锁相环器件选用ADI公司的ADF4112芯片,该芯片集成了鉴相器和可编程分频器,最大工作频率为3GHz,相位噪声基底可达-215 dBc/Hz。VCO采用Crystek公司的CVC055BE-1530-2700,其频率范围为1530~2700MHz,灵敏度为140MHz/V,输出功率65dBm,相位噪声-87dBc/Hz@10kHz。

环路滤波器的设计是频率合成器设计的最重要的一个部分,它的性能好坏直接关系到锁相输出的相位噪声和杂散指标。由于本系统输出频带范围比较大,VCO所需的控制电压最高达到7.5V,高于所选锁相环芯片中电荷泵所能提供的最高供电电压,所以使用无源环路滤波器不足以达到控制VCO所需的调谐电压值,必须使用具有放大功能的有源滤波器。为了抑制有源器件产生的噪声,一般使用三阶以上的有源环路滤波器,电路如图2中所示。这种结构采用同相放大器,不需要专用偏置,比较直观、简便。电阻R3和R4用来控制电路的增益,增益大小A表示为:

![]()

而且,电阻R4和R3的取值必须足够大,以保证其消耗的电流不超出范围。C3和R2有边带滤波作用,C1、C2和R1则用来调整环路带宽、阻尼系数、相位噪声等参数。

其中运算放大器采用ADI公司的AD820,该运算放大器具有可单电源供电、轨到轨、低噪声等特点,满足本设计的要求。系统整体电路图如图2所示。