・上一文章:警用旋翼机数据处理及传输系统设计

・下一文章:数字系统的电源去耦设计

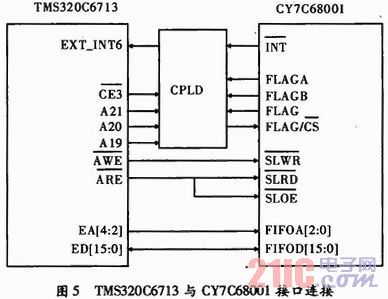

CY7C68001除了存储器接口外,还有1个中断信号![]() 和4个状态信号。中断信号

和4个状态信号。中断信号![]() 采用TMS320C6713的外部中断EXT_INT6。

采用TMS320C6713的外部中断EXT_INT6。

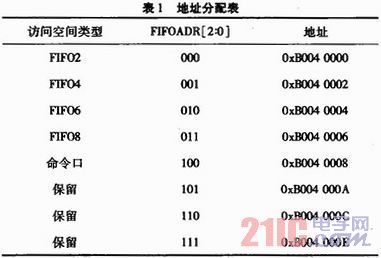

TMS320C6713使用CY7C68001作为从设备。在这种模式下,DSP可以像读/写普通FIFO一样对CY7C68001内部的FIFO进行读/写。PC主机发出命令的同时也由CY7C68001 ![]() 的引脚提供中断触发信号给DSP的EXT_INT6。其上升沿被检测到后,DSP就进入相应中断服务程序,开始处理USB的传输。DSP通过EA[4:2]连接FIFOA[2:0]对CY7C68001内部FIFO或命令口进行选择。读/写数据通过ED[15:0]与FIFO[15:0]连接进行。FIFO和命令口的选择和地址分配如表1所示。

的引脚提供中断触发信号给DSP的EXT_INT6。其上升沿被检测到后,DSP就进入相应中断服务程序,开始处理USB的传输。DSP通过EA[4:2]连接FIFOA[2:0]对CY7C68001内部FIFO或命令口进行选择。读/写数据通过ED[15:0]与FIFO[15:0]连接进行。FIFO和命令口的选择和地址分配如表1所示。

经实验验证,USB异步传输速率可达3 Mbit·s-1,满足系统需求。

1.6 PC机平台

DSP数据处理模块通过USB接口与PC机相连,通过CY7C68001芯片,将前端采集的数据传输到PC机,方便对数据的进一步处理。

2 程序设计

2.1 McASP接口程序设计

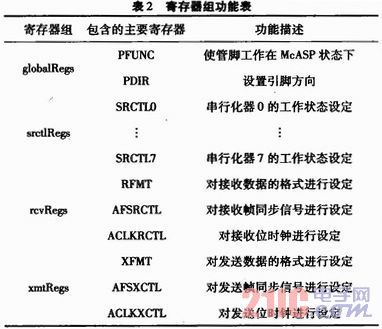

定义了4个寄存器组:全局寄存器组globalRegs、发送寄存器组xmtRegs、接收寄存器组mvRegs和串行化器控制寄存器组SRCtlRegs。通过这4个寄存器组,对McASP1的PFUNC,PDIR,SRCTL,RFMT,AFSRCTL,ACLKRCTL及AHCLKRCTL等寄存器进行设置。各寄存器组所包含的主要寄存器情况如表2所示。