����������һ�������Ĺ�˾�����dz�֮ΪNEWCO��˾���������������ǵĵ�һ̨�����������ľ�ԭ�ͻ������Ǿ���ʹ�õ�Ե��������Ա�������ӡˢ��·��ķ��ú�ʱ�䡣ԭ�ͻ�����16IN/20IN�ĵ�·����ͨ�������ƽӼ����������ġ���һ��ԭ�ͻ�����600����ŵ�·��2000����ͬ���ź����硣�������й��ź������һЩ�����ݣ�

�������Ŀ��2000

�����ƽ�����ȣ�40IN��δ�˽ӵģ�

�����ڽӵ�ƽ���Ϸ���ƽ���߶ȣ�0.2IN

�߾���AWG30����0.01INֱ��

�ź�����ʱ�䣺2.0NS

ת��Ƶ�ʣ�250MHz��=0.5/2.0NS��

1����Ե㲼�ߵ��źŻ���

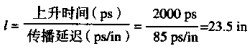

��NEWCO������У�����ʱ��Ϊ2.0NS�����������Ϊ��

���ּ���ϵͳ�ͷֲ�ϵͳ���ٽ�ߴ��ǣ�1/6=3.9IN

NEWCO��Ϊ����Ϊ���ߵ�ƽ�����Ȼ���������һ����֮�ڣ����Ե�·ֻ���к��ٵ����塣�������Ǵ��ˡ�

NEWCO��ʶ��������·����1/6ʱ�������ֲַ�״̬������֪�����ֲ���·������˽ӣ��ͻ����塣��Ϊ���ǵĵ�·�Ǽ��ܵģ����Դ������Ϊ�������塣

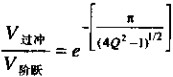

���ܲ�����·�������壬Ҳ���ܲ����壬��ȡ���ڵ�·��Qֵ����·��Qֵ��ʾ����·���ź�˥�����ŵĿ������ڵ�Qֵ��·�У��ź�˥���úܿ죬���ڸ�Qֵ��·�У��ź�ȴ���������������������ں�����������š�Qֵ�ڼ����ϱ�����Ϊ�ܴ洢������ÿ����������˥������֮�ȡ��������������һ�����ƹ�ʽ�����ض���·���������ѹ��Qֵ��һ����������ʾ��

���У�V����=������̬�����ƽ�������������V

V��Ծ=Ԥ�ڵ���̬��ƽ��V

Q=г�������������詃0.5��

ͼ4.1�е��������·��ʱ�䳣��2L/R˥������ȫ������ʽ��

���ݾ��飬��һ�������Ծ��������Ӧ�У�QֵΪ1�����ֵ�·��ʾ��16%�Ĺ��壬QֵΪ2�����ֵ�·����ʾ��44%�Ĺ��塣�κ�Qֵ����1/2�ĵ�·�������������塣һ����·�ϲ����������ǵ�·�����Ĺ���г��Ƶ�ʺ�����������ʱ��֮���ϵ��һ������������Ҳ���о�������⡣

һ������֪���˵�·�ĵ�У�����һ�����ֵ�·��Qֵ�Ǻ����ġ�����ʾ���ǹ�ע��Ե㲼�ߵĻ������⣺�ߵ�С�

��һ���ߵ�����߹����ڴ���ݸ��ص������ʱ�����γ�һ����Qֵ�ĵ�·��

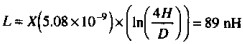

���ǿ��Բ��ø�¼C���г��Ĺ���һ��λ�ڽӵ�ƽ��֮�ϵ�Բ���嵼���㹫ʽ�������NEWCOϵͳ��һ����������ĵ��L��

���У�L=��·��У�H

D=�ƽ��ߵ�ֱ����0.01IN

H=��·�ڽӵ�ƽ���ϵĸ߶ȣ�0.2IN

X=�ߵij��ȣ�4IN

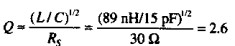

����ʽ�� �������Լ������������Դ�˵��衢���ߵĴ�����кͽ������ĸ��ص�����ɵ�RLC��·��Qֵ��

�������Լ������������Դ�˵��衢���ߵĴ�����кͽ������ĸ��ص�����ɵ�RLC��·��Qֵ��

R=30ŷ��һ��TTL��������������裩

L=89NH��ƽ�����ߵ�У�

C=15PF�������أ�

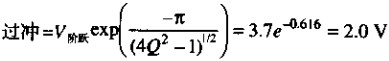

QֵΪ2.6��ζ�ţ�����һ������Ľ�Ծ���룬���õ���С�����塣��ʽ������Ԥ�������Ĺ����ѹΪ��

V��Ծ=3.7V��TTL��Ծ�����

Q=2.6��������ʽ��

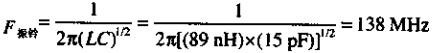

ֻ�е�NEWCO����������������Ƶ�����ϴ�����Ч����ʱ����������Ĺ���Żᷢ����������ʽ�����ҳ�����Ƶ�ʣ�

Ƶ���ȵĺ�������ת��Ƶ�ʣ�����ʽ�����Ķ��壬NEWCO�����ŵ�·ת��Ƶ�ʣ�250MHZ��ԶԶ��������Ƶ�ʣ�138MHZ����������ڴ����ĵ��ܣ���������������̡�ת��Ƶ��������õ���138MHZ������ͽ���С��Լһ�롣ת��Ƶ�ʸ��͵����ŵ�·���������廹���С��

�����ȫ��ʱ���п��ǣ����ǿ��Զ϶���������ʱ������������ڵ�һ��ʱ�������µ����屻����һ�롣����ʱ��Խ�������������ԽС���෴��������ʱ��ԶԶС���������ڵ�һ��ʱ�������������µ����塣

���ǿ��Դ�Qֵ�����з��ָ�����۾ݡ�����֪����NEWCO�ĵ�·һ����138MHZƵ�����壬������Ϊ2.0V���������Ե�·���ۿ���֪������Ĺ������Ƿ����ڽ�Ծ���غ��������ڵĶ���֮һ������ˣ���Ԥ֪�����彫�ᷢ����ÿ����ת�����3.6NS����