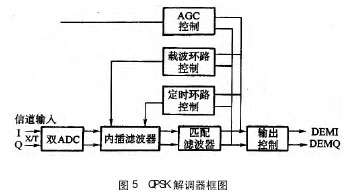

答:(1)QPSK解调器主要包括时钟产生电路、QPSK(四相相移键控)解调器、前向纠错(FEC)单元和输出控制电路等部分。时钟产生电路为 PLL 频率合成器,首先由外部晶体振荡产生基准时钟,再由集成在片内的 VCO 分频产生解调和 FEC 所需的各种时钟。QPSK 解调器由匹配滤波器、数字振荡器、定时时钟恢复环路、载波恢复环路、自动增益控制(AGC)电路等组成,如图 5 所示。

匹配滤波器为平方根升余弦滤波器,该滤波器工作在 2/T 的恒定输入速率上。时钟恢复环路包括 I、Q分量内插滤波器和定时误差检测器,定时误差检测器用来捕获时钟信号,内插滤波器确定环路特性和数字振荡器(NCO)的增益。

载波恢复环路由相位误差检测器、数字环路滤波器、相位环路检测器、频率扫描发生器和频率锁定指示器组成。QPSK 解调芯片内有两个嵌入的数字自动增益控制(AGC)电路,第一个 AGC 与片外的 RC 滤波电路组成宽带 AGC 电路,产生脉宽调制信号输出到调谐器,使调谐器的增益受此信号控制。第二个 AGC 为数字窄带AGC,主要完成数字信号带宽的功率最优化。

(2)QPSK 解调时,D/A 转换器输出的 I、Q 信号中的基带信号以固定采样速率输入到 QPSK 解调器中的载波恢复环路。相位误差检测器使用由信噪比决定的两种增益完成误差检测,进行载波相位跟踪。

此时频率扫描发生器搜索正确的载波频率,当载波频率接近输入信号频率时,载波信号进入相位锁定范围,环路达到锁定状态,实现载波捕获。载波恢复环路通过捕获载波和跟踪载波相位完成载波恢复,解出基带信号。该信号送到匹配滤波器,由匹配滤波器在 I、Q 分支上选择滚降因子 (0.35)来完成匹配滤波,匹配滤波器始终保持每 4 个符号采样一次。

当符号速率较低时,采用较多的采样次数;当符号速率较高时,采用较少的采样次数。匹配滤波器的输出端接有一个精度达 0.5 dB 的数字窄带 AGC 电路,使 QPSK 解调器输出的信号以最优的均分送到 FEC 单元。

(3)FEC 单元包括 Viterbi 解码器、去交织器和里德—索罗门解码器。Viterbi 解码器用于内码解码,支持 1/2、2/3、3/4、5/6、6/7、7/8 的收缩码率。去交织器完成卷积去交织处理,处理的最大块长度为 204 字节,交织深度为 12。