・上一文章:视频会议多点控制单元的MCU设计与实现

・下一文章:基于LabVIEW的摩擦磨损试验机智能测控系统

2 系统硬件平台

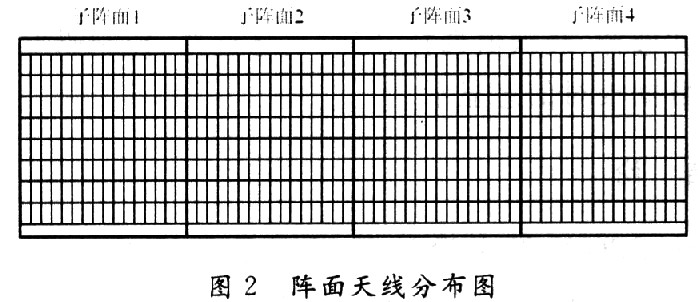

该相控阵雷达系统要求波束控制系统准确可靠地控制512个天线单元,波束转换时间不大于1 ms。在此分析运算板需要哪些关键器件。运算板要在500μs内完成从雷达控制台接收指令、波束控制算法及运算结果传输的功能,必须选用FPGA器件。参与运算的补偿数据是运算的主要对象之一,要能够实时参与波束控制算法的运算过程,也可以被雷达控制台在线更新,这就需要运算板具有存储器。系统采用自定义总线接收雷达控制指令和上报阵面返回的信息。

关于驱动板的硬件设计,不仅要实现驱动、译码、系统自检等功能,还要考虑组件在单独调试时驱动板的控制功能是否可以方便实现。由于设备数量较大,在满足功能的基础上,要尽可能降低设备成本。基于这些需求,选用一片单片机和一片EPLD。图1中虚线左侧部分所示运算板硬件组成。其中,雷达控制台发送的是波束控制指令、接收的是阵面自检和检测信息;传输模块产生和发送串行波束控制码、传送所需要的时钟、定时信号。

图l中虚线右侧部分所示组件驱动板的硬件组成。其中接口电路接收波束控制运算板发来的串行波束控制码;组件单元接收的是TTL电平的控制码(包括发射移相码、接收移相码、衰减码、T/R开关控制码)。EPLD完成译码和控制分发代码,SCU完成联机自检和脱机控制调试的功能。控制和调试方式比其他提供的系统设计方法,更加多样化和灵活。

3 软件设计

3.1 运算板FPGA程序设计

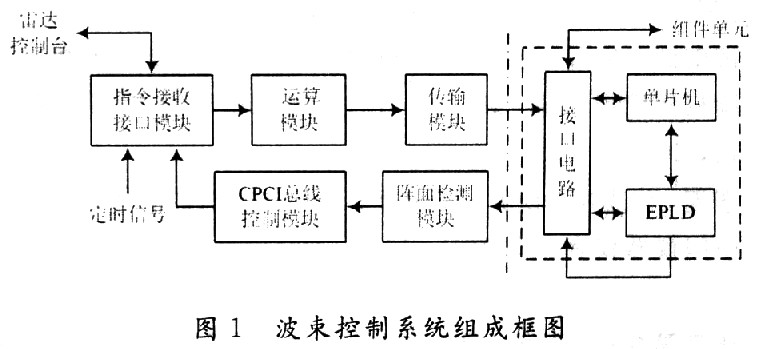

波控运算板基本用途就是为满足阵面天线单元控制的需要。在此,整个天线阵面等分成四个子阵面。每个子阵面包括a×b个天线单元,如图2所示。