・上一文章:PCB Matrix IPC-7351 LP软件介绍及使用说明

・下一文章:Quamtum-SI DDR3仿真解析

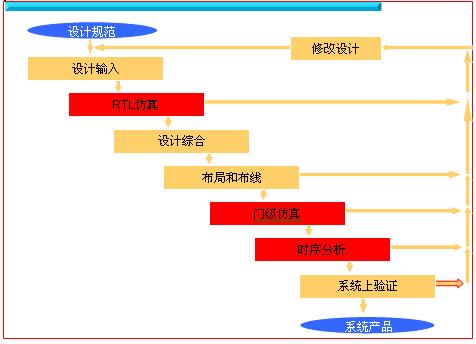

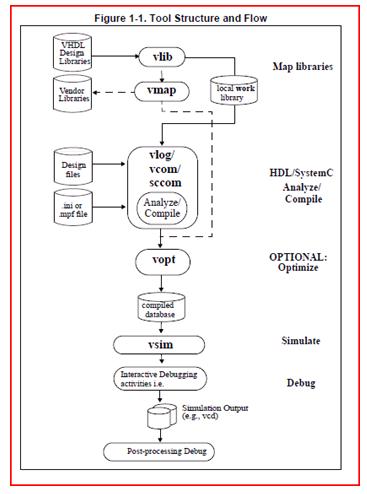

ModelSim支持RTL仿真,门级仿真,时序仿真:

主要特点:

*采用直接编译结构,编译仿真速度最快;

*单一内核无缝地进行VHDL和Verilog混合仿真;

*与机器和版本无关,便于数据移植和库维护;

*与机器无关的编译代码编于保护和利用IP;

*简单易用和丰富的图形用户界面,快速全面调试;

*Tcl/Tk用户可定制仿真器;

*完全支持VHDL/Verilog国际标准,完全支持Verilog 2001;

*支持众多的ASIC和FPGA厂家库;

*集成的Performance analyzer帮助分析性能瓶颈,加速仿真;

*灵活的执行模式,Debug模式可以进行高效的调试,效率模式大幅度提高仿真速度。

*加强的代码覆盖率功能Code coverage,能报告出statement 、branch、condition、

* expression、toggle、fsm等多种覆盖率情况,进一步提高了测试的完整性;

*同一波形窗口可以显示多组波形,并且能进行多种模式的波形比较(Wave Compare);

*先进的Signal Spy功能,可以方便地访问VHDL 或者 VHDL 和Verilog 混合设计中的下层模块的信号,便于设计调试;

*支持加密IP;

*集成的 C调试器,支持 用C 语言完成测试平台和模块;支持64位的OS;

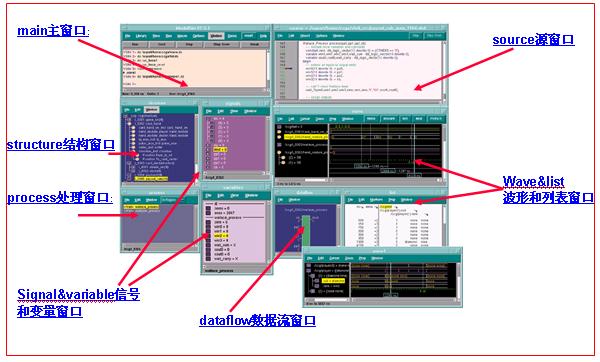

ModelSim用户界面:

ModelSim设计流程:

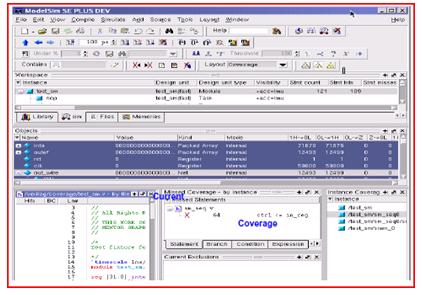

ModelSim coverage验证: