2.3 JTAG电路

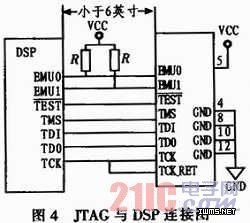

JTAG是基于IEEE 1149.1标准的一种边界扫描测试方式(Boundary-sCAN Test),结合仿真器和仿真软件,可访问DSP的所有资源,包括片内寄存器以及所有的存储器,从而提供实时的硬件仿真与调试环境,便于开发人员进行系统调试。在大多数情况下,如果开发板和仿真器之间的连接电缆不超过6英寸,可以采用图4的接法。但应该注意,DSP的EMU0和EMU1引脚都需要上拉电阻,推荐值为4.7 kΩ或者10 kΩ。如果DSP和仿真器之间的连接电缆超过6英寸,则需要另加缓冲驱动电路。

2.4 时钟电路

TMS320VC5509的外部时钟从CLKIN引脚输入,在内部修改这个信号,来产生希望频率的输出时钟,时钟发生器将这个输出时钟(即CPU时钟)送给CPU、外设和其他的内部模块。也可以用可编程的时钟分频器对CPU时钟分频,在CLKOUT引脚输出。时钟发生器中还有一个时钟模式寄存器(CLKMD),用来控制和监视时钟发生器,它可以控制时钟发生器进入两种工作模式:

1)旁路模式,PLL被旁路掉,输出时钟的频率就等于输入时钟的频率除以1、2、4。

2)锁定模式,输入时钟既可以乘以或除以一个系数来获得期望的输出频率,并且输出时钟相位与输入信号锁定。

在锁定模式下,输出频率由下面的公式计算:

输出频率=(PLL MULT/(PLL DIV+1))×输入时钟频率

在此,可以选择时钟发生器工作在锁定模式,即CLKMD的PLL ENABLE为1,外部振荡晶体可以为10~20 MHz。根据外部振荡晶体与DSP内部时钟信号,可以计算出相应的PLLMULT与PLL DIV值,图5为DSP的外部时钟电路。