摘要:为了实现DSP芯片与串行A/D芯片的多信号通信,设计了TMS320F28335的多通道缓冲串口(McBSP)与串行A/D转换器ADS7863的硬件与软件接口。该设计中A/D转换器与McBSP串口直接相连,不需要占用并行数据总线,避免了总线冲突。通过在CCS环境下鳊程、调试,得到了满意的实验结果,验证了该接口设计的正确性。

关键词:TMS320F28335;A/D转换器;ADS7863;多通道缓冲串口

引言

近年来,DSP技术发展迅速,越来越多的工程技术人员开始采用DSP进行系统设计。TI公司的TMS320F28335具有运算速度快、功耗小和性价比高的特点,在个人通信、信号与信息处理及自动控制等领域得到了广泛应用。该芯片配备了两个多通道缓冲串口(Multi-channel Buff-ered Serial Port,McBSP),为设计串行模数接口提供了极大的便利。它与串行A/D转换器构成的信号采集与处理系统具有硬件设计简单、可靠性好的特点。本文将阐述TMS320F28335与ADS7863的接口设计。

1 TMS320F28335 McBSP

1.1 TMS320F28335 McBSP的特点

TMS320F28335是一款高性能、多功能、高性价比32位浮点DSP。该器件最高可在150 MHz主频下工作,片上集成丰富的外设,其中包括两个多通道缓冲串口(McBSP)。McBSP是一种同步串行接口,除具有一般DSP串口功能之外,还可以支持T1/E1,ST-BUS,SPI等不同标准。它的主要特点如下:全双工串行通信;允许独立数据流的双倍发送缓冲和三倍接收缓冲数据存储器;独立的接收、发送帧和时钟信号;发送和接收通道数最多可达128路;多通道选择模式,允许或阻止每个通道的传输;两个16级,32位的FIFO代替DMA;可直接与工业标准的编码器、模拟界面芯片(AICs)、其他串行A/D,D/A器件连接;支持时钟信号和帧同步信号的外部生成;用来内部生成和控制帧同步信号的可编程采样率发生器;可编程的内部时钟和帧同步信号生成;可编程的帧同步和数据时钟极性;可选的数据宽度:8 b,12 b,16 b,20 b,24 b或32 b;比特数据传输时可选择高位或低位在先;用于数据压缩的μ律和A律压缩扩展。

1.2 TMS320F28335 McBSP的工作过程

TMS320F28335的McBSP包括7个引脚,分别是串行数据发送信号DX,串行数据接收信号DR,发送时钟信号CLKX,接收时钟信号CLKR,发送帧同步信号FSX、接收帧同步信号FSR和外部输入时钟信号CLKS。McBSP通过这7个管脚为外部设备提供了数据通道和控制通道。

McBSP通过DX和DR实现DSP与外部设备的通信和数据交换。其中,DX完成数据发送,DR完成数据接收。控制信息通过CLKX,CLKR,FSX和FSR以时钟和帧同步的形式进行通信。由于McBSP内有一个可编程的采样和帧同步时钟发生器,所以这些时钟和帧同步信号既可以由内部产生,也可以由外部输入。

McBSP发送数据的过程如下:首先将要发送的数据写入数据发送寄存器DXR[1,2],如果发送移位寄存器XSR[1,2]中没有数据,则DXR[1,2]中的值先复制到XSR[1,2],再由XSR[1,2]将数据移到DX上发送;如果XSR[1,2]不为空,则等待将XSR[1,2]中的数据全部移出到DX脚发送后才将DXR[1,2]中的值复制到XSR[1,2],再由DX脚将数据发送出去。

McBSP接收数据的过程如下:DR脚上接收的数据首先移入接收移位寄存器RSR[1,2],一旦收到一个字(可以是8 b,12 b,16 b,24 b或32 b),检查接收缓冲寄存器RBR[1,2]是否为空,如果为空,则将RSR[1,2]中的数据复制到RBR[1,2],接着,数据被复制到数据接收寄存器DRR[1,2],CPU通过读取DRR[1,2]中的数据完成数据接收。需要注意的是,DRR2,RBR2,RSR2,DXR2和XSR2寄存器只有当接收或发送的字

长超过16 b(20 b,24 b和32 b)时,才会用上。

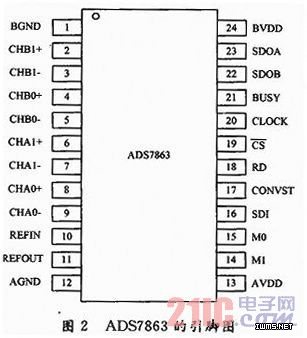

0位数据延迟时,McBSP串口接收和发送数据的时序图如图1所示。

2 ADS7863

2.1 ADS7863芯片的特点

ADS7863是一个双路、2 MSPS、12位、3+3或2+2通道、同步采样模/数SAR转换器。ADS7863具有如下特点:四路全差分或六路伪差分输入;SNR:71 dB,THD:-81 dB;可编程的和缓冲的内部2.5 V参考电压;灵活的省电功能;可变的电源范围:2.7~5.5 V;低功率操作:5 V时45 mW;工作温度范围:-40~+125℃;引脚与ADS7861,ADS8361兼容。

2.2 ADS7863芯片的工作原理

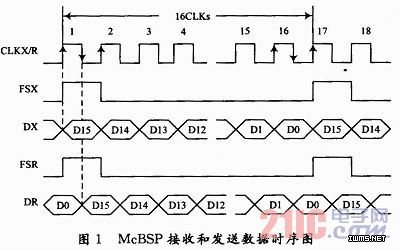

ADS7863的引脚图如图2所示。