・上一文章:LTE中RRM功能及架构分析

・下一文章:三分量磁通门传感器非正交性误差校正

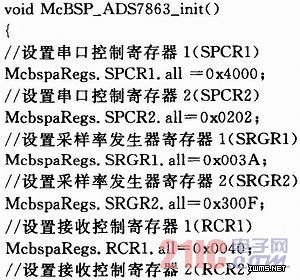

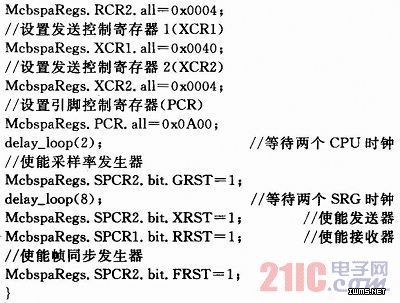

3.2 软件接口设计

3.2.1 McBSP口初始化

整个初始化过程包括三部分:接收部分初始化、发送部分初始化和采样率发生器初始化。

(1)DSP初始化后,采样率发生器的初始化位GRST=0;在其他情况下,也可通过向SPCR2寄存器中的GRST位置0,使采样率发生器处于初始化状态。在此状态下,时钟CLKG时钟为CPU时钟的1/2,帧同步信号FSG为逻辑0;设置接收初始化位RRST、发送初始化位XRST和帧同步发生器初始化位FRST为0;

(2)对采样率发生器SRGR[1,2]进行设置,并对其他控制寄存器进行设置;

(3)等待两个CPU时钟以确保内部正确同步;

(4)将采样率发生器初始化位置1,使采样率发生器进行工作;

(5)等待两个SRG时钟;

(6)将接收和发送初始化位置1;

(7)在下一个CPU时钟的上升沿,CLKG时钟发送一个1,并以CPU时钟/(1+CLKGDV)的频率运行;

(8)在数据发送寄存器DXR[1,2]被载入数据后,将帧同步初始化位置1以发出正确的帧同步脉冲信号。

下面是McBSP初始化程序片段: