・上一文章:基于51单片机智能排插的设计与实现

・下一文章:TI KeyStone 架构支持 L2 与传输处理

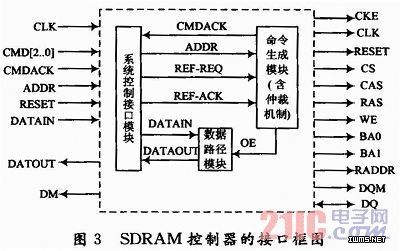

下面对接口信号进行介绍:与主机接口信号有CLK:系统时钟信号;RESET:系统复位信号;CMD[2:0]:译码指令;CMDACK:指令应答信号,通知主机命令已被SDRAM执行;ADDR:地址线,该设计中为22位,A21,A20代表页地址BA1,BA0;A19~A8代表行地址;A7~A0代表列地址;DATAIN/DATAOUT:输入、输出数据总线;DM:数据掩码。与SDRAM接口信号有RADDR:12位地址线,在读/写操作时,地址线时复用为行地址和列地址;BA0,BA1页地址选择;CS:片选信号;CKE:时钟使能信号;RAS,CAS,WE:命令控制信号;DQM:SDRAM数据掩码;DQ:双向数据线。SDRAM控制器作为顶层模块,内部由3个主要模块构成:系统控制接口模块、命令生成模块和数据路径模块。系统控制接口模块用于接收系统的控制信号,进而产生不同的CMD命令组合;命令用于接收CMD命令并解码成操作指令并产生SDRAM的操作动作;数据通路模块则用于控制数据的有效输入/输出。

使用SDRAM的目的是进行数据传输,即要求能正确地读写数据。因此,在SDRAM操作过程中,最重要是就是初始化、读和写的操作,因此,本文完成了SDRAM初始化在QuailtusⅡ仿真下的时序波形图,如图4所示。