在写数据时仅能使对应单元的数据位由“1”变为“0”,而从“0”变为“1”只有擦除命令才能完成。擦除操作可以按扇区擦除也可以对整个芯片擦除。因此在设计时可将程序代码和常量表等固定数据和系统动态更新数据分开存放。每次向更新数据区写数据前对该区数据进行擦除操作即可。

在擦除和写操作之后,就可以读数据了,读数据的操作非常简单,由0E#,CE#控制,当这两个信号为低电平时,在地址线上输入地址,数据线上就可以读出数据了。

当按照规定的命令序列向FLASH存储器发出命令时,其内嵌的算法状态机会自动地完成相应的操作。但用户还应了解其内部的操作检测机制,以便知道操作是否完成,以及操作是否正确。该芯片的状态检测位有:数据查询位DQ7,TOGOLE位DQ6和DQ2。通过查询它们对应的状态,即可知道芯片的工作状态。

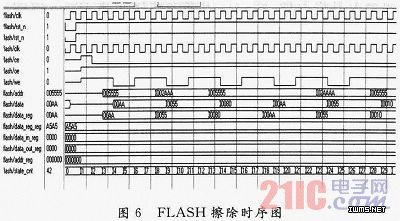

在编程实现时,用状态机实现FLASH的接口控制,要确保数据线和地址线的建立和保持时间满足需求,严格确保实际提供的时序和硬件要求一致。图6为在ModelSIM仿真下的FLASH的擦除时序图。

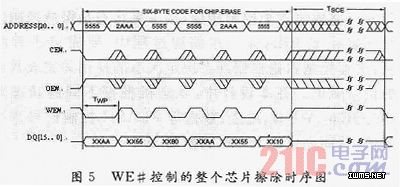

整个程序的编程实现是用有限状态机来实现的。以擦除为例,介绍有限状态机的设计方法。状态控制借助系统时钟进行,通过多个状态来完成ERASE操作。状态0初始化各输出信号,状态1~5完成第一个命令输入,状态7~10完成第二个命令的输入,状态12~15完成第三个命令的输入,状态17~20完成第四个命令的输入,状态22~25完成第五个控制命令输入,状态27~30完成第六个控制命令,接下来状态是保持控制信号用来完成ERASE。在编程过程中,要完成进程控制:进程控制就是根据现态决定次态的控制并完成其他的信号赋值。在本设计中,状态机根据不同的状态对CE、OE#、WE#、地址、数据等FLASH控制信号进行赋值,从而完成对Flash的控制。

但是每执行1次写操作,只能写入1个地址单元里的字数据,如果按照这个方法,完成整个FLASH芯片2 MWord的数据写入就需要重复执行写操作2兆次,这样既麻烦又浪费时间。在实际操作中,通常通过计算机上的图形界面来完成FLASH的烧写工作,通过图形界面使单片机把计算机存储的数据暂存在SDRAM,然后通过一个判断语句检测SDRAM是否存满,没有存满则继续存储,如果存满则通过FPGA控制把SDRAM上的数据存储在FLASH上,这样通过一次操作即可存满。

3 结语

本文介绍了FPGA外部存储器的设计方法,可以有效地解决雷达实时信号处理过程中海量数据的存储问题,同时也可以充分利用FPGA去控制SDRAM和FLASH,不仅保证了资源的充分利用,也可以有效地满足信号处理过程中的高速实时的要求。另外,可以根据FPGA型号的不同,适当地更改外部存储器,以满足不同的应用场合。