系统工作时,在激励信号的驱动下,磁通门探头的感应线圈感应环境磁场大小,产生磁通门信号,经隔直滤波后通过高速ADC芯片转换成串行数据送FPGA的处理。在FPGA中,ADC芯片采集到的串行数据先转换成并行数据,然后通过相敏整流、低通滤波后得到直流信号。低通滤波的结果积分放大后经D/A接口转换成串行数据送高速DAC芯片转换成模拟信号,经反馈电阻反馈到磁通门探头的补偿线圈(即感应线圈),抵消环境磁场。

由于采用闭环结构,前向通道上积分放大环节的增益可视作无穷大,根据自动控制原理,整个系统是无差系统,传感器探头实际上工作在“零场”条件下,反馈电流产生的磁场和环境磁场大小相的方向相反,D/A的前端信号,即积分放大环节的输出反映被测磁场的大小。整个系统的信号梯度主要取决于反馈系数的大小,具有良好的线性度。

2 磁通门信号的特点和处理方法

磁通门系统的核心是信号处理电路。

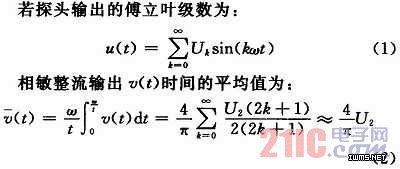

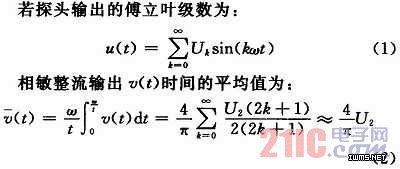

磁通门传感器探头输出的偶次谐波(以二次为主)是有用的磁通门信号,而其他频率的信号都是有害噪声。在实际应用中,通常采用“相敏整流-低通滤波”方法处理磁通门信号。首先用相敏整流进行频谱的调整,通过采用与二次谐波同频率的方波基准乘传感器探头的输出,将二次谐波磁通门信号转换为直流分量,然后用低通滤波滤除其他频率分量,得到反映被测磁场大小的直流量。

低通滤波器输出是相敏整流结果的直流分量,与磁通门传感器探头输出的二次谐波的幅值线性相关,反映被测磁场大小。

3 硬件电路设计

在该设计中,FPGA芯片选用ALTEra公司CYCLONEⅡ系列的EP2C35F626C5,工作速度快,可定义引脚丰富,逻辑单元数量可观,性价比高。FPGA的工作时钟为50 MHz。

磁通门激励起到驱动传感器工作的作用,由D/A模块转换FPGA输出的正弦数字信号产生;本设计中,激励频率为3.051 kHz,是FPGA工作时钟的64×256分频,速度相对较低,且精度要求不高,故DAC采用12位并口DA1210芯片。

在闭环系统的前向通道中,A/D模块是偏差检测环节,对传感器探头输出进行采样。该设计中,二次谐波一个周期采样128个点,即ADC采样频率是探头输出二次谐波频率的128倍,也就是781.25 kHz。采用AD7980芯片作为A/D转换器,该芯片具有16位精度,转换速度高达1 MSPS,可以满足要求。

在反馈回路中,D/A模块作为低频补偿环节,需要具有较高的精度,而转换速率可以较低;该设计采用DA8552芯片,具有16位精度和100 KSPS的转换速率。

4 FPGA内部电路设计

4.1 A/D接口和D/A接口

由于前向通道的ADC芯片、反馈回路的DAC芯片都采用串口通信,因此设计了专用的A/D接口和D/A接口,实现了A/D输入和D/A输出的串并/并串转换。

4.2 正弦激励发生

正弦激励发生采用查表的方式实现。用12×256b的ROM存一幅12位正弦波表,以FPGA时钟频率的1/64,即781.25kHz扫描,产生3.051 kHz的12位数字正弦信号。

上一页 [1] [2] [3] [4] 下一页