・上一文章:基于ADIS16365的惯性传感系统设计

・下一文章:基于D-S证据理论的多传感器数据融合

4.3 磁通门信号解算和积分放大

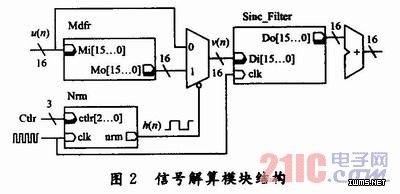

磁通门信号的解算是FPGA内数字逻辑最核心的功能,由相敏整流器、基准发生器和FIR数字滤波器三部分共同实现,如图2所示。

相敏整流器由数据转换器和数据选择器构成。数据转换器.Mdfr将输入u(n)转换成补码形式。输出v(n)是输入u(n)或者其补码,由基准h(n)当前的值决定。实际上,电路的功能等价于将u(n)和在1和-1间交替变化的数列相乘,也就是说,v(n)是u(n)以h(n)为基准相敏整流的结果。

基准发生器Nrm为相敏整流器提供基准h(n)。对50 MHz时钟进行分频,产生与二次谐波磁通门信号同频率,即6.103 MHz的方波,通过控制信号Ctlr调整相位,使基准的相位和二次谐波磁通门信号的相位对其相敏整流的效率最大化。

低通滤波器Sinc_Fltr是N点sine滤波器的FIR形式,传输函数是:

信号流图如图3所示。

由于二次谐波磁通门信号一个周期采样128点,因此N=128;按照图3所示的信号流图,128点sinc滤波器由127个加法器和128个寄存器组成。为防止溢出,加法器和寄存器宽度为16+log2 8=24位,最后一级输出的高16位作为滤波器的输出。实现了低通滤波的功能。

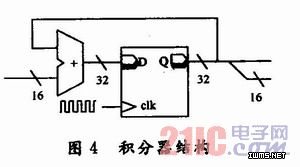

积分放大由积分器Intgtr实现,结构如图4所示。为防止溢出,采用32位的加法器和寄存器。加法器的一个输入端是低通滤波器的输出,另一个是累加和。在闭环系统中,积分器输出的低16位是反映被测磁场大小的数字量。