对于高速ADC,若要最大程度地提高SFDR,存在两个基本限制:第一是前端放大器和采样保持电路产生的失真;第二是ADC编码器部分的实际传递函数的非线性所导致的失真。

提高SFDR的关键是尽可能降低以上两种非线性。

要显着降低ADC前端引起的固有失真,在ADC外部着力是徒劳的。然而,ADC编码器传递函数的微分非线性可以通过适当利用扰动(即外部噪声,与ADC的模拟输入信号相加)来降低。

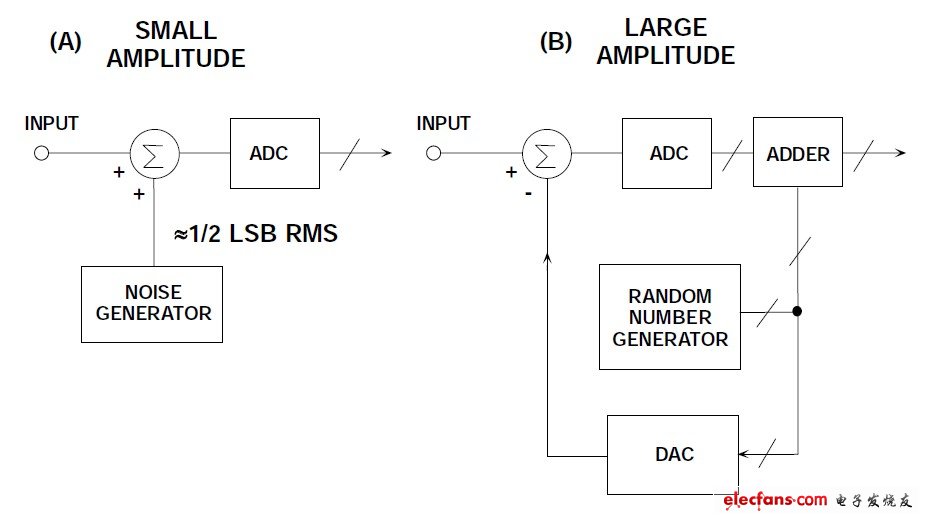

在一定的条件下,扰动可以改善ADC的SFDR(参考文献2-5)。例如,即使在理想ADC中,量化噪声与输入信号也有某种相关性,这会降低ADC的SFDR,特别是当输入信号恰好为采样频率的约数时。将宽带噪声(幅度约为? LSB rms)与输入信号相加往往会使量化噪声随机化,从而降低其影响(见图5A)。然而,在大多数系统中,信号之上有足够的噪声,因此无需额外添加扰动噪声。ADC的折合到输入端噪声也可能足以产生同样的效果。将宽带均方根噪声电平提高约1 LSB以上会成比例地降低ADC SNR,且性能不会有进一步的提高。

还有其它一些方案,都使用更大数量的扰动噪声,使ADC的传递函数随机化。图5B还显示了一个由驱动DAC的伪随机数发生器组成的扰动噪声源,此信号从ADC输入信号中减去后,以数字方式增加到ADC输出中,从而不会导致SNR性能显着下降。这种技术本身有一个缺点,即随着扰动信号的幅度增大,允许的输入信号摆幅会减小。之所以需要减小信号幅度,是为了防止过驱ADC.应当注意,这种方案不能显着改善ADC前端产生的失真,只能改善ADC编码器传递函数的非线性所引起的失真。

图5:利用扰动使ADC传递函数随机化

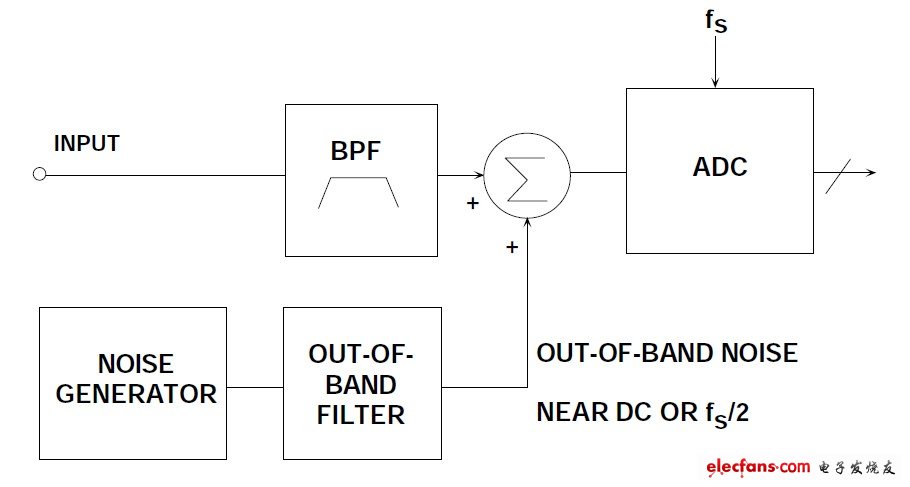

还有一种方法更容易实现,尤其是在宽带接收机中,即注入信号目标频带以外的一个窄带扰动信号,如图6所示。一般来说,信号成分不会位于接近DC的频率范围,因此该低频区常用于这种扰动信号。扰动信号可能还位于略低于fs/2的地方。相对于信号带宽,扰动信号仅占用很小的带宽(数百kHz带宽通常即足够),因此SNR性能不会像在宽带扰动下那样显着下降。

图6:注入带外扰动以改善ADC SFDR

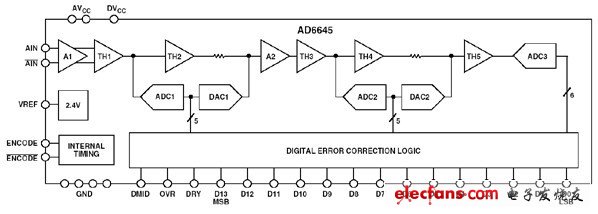

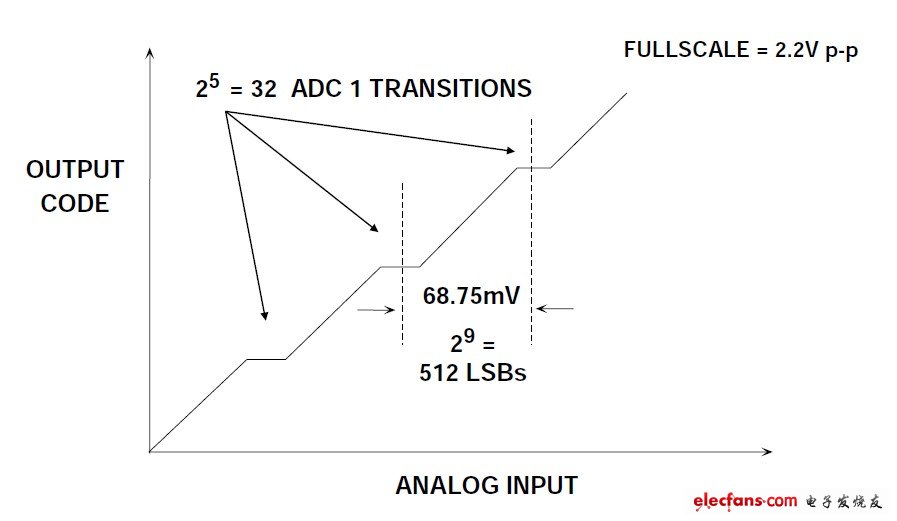

分级流水线式ADC,例如图7所示的14位105 MSPS ADC AD6645,在ADC范围内的特定代码跃迁点有非常小的差分非线性误差。AD6645由一个5位ADC1、一个5位ADC2和一个6位ADC3组成。严重的DNL误差仅出现在ADC1跃迁点,第二级和第三级ADC的DNL误差非常小。ADC1有25 = 32个相关的决策点,每隔68.75 mV (29 = 512 LSB)出现一个(2.2 V满量程输入范围)。图8以夸张形式显示了这些非线性误差。

图7:14位105 MSPS ADC AD6645简化框图

图8:AD6645分级点DNL误差(夸张显示)