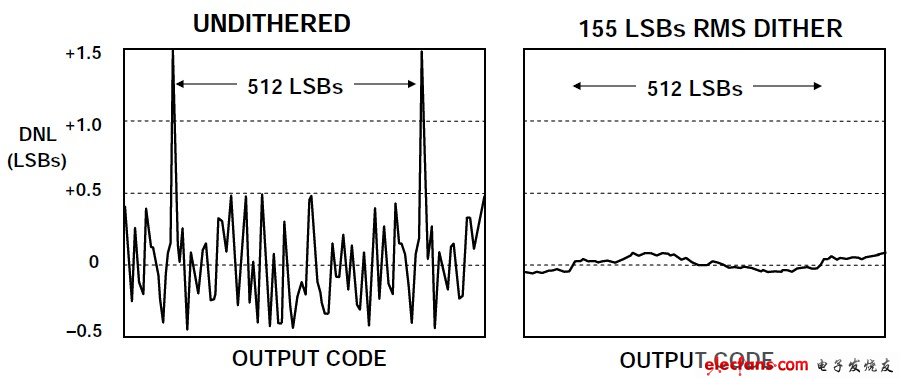

目标是选择适当的带外扰动量,使得这些微小DNL误差的影响在ADC整个输入范围内随机化,从而降低平均DNL误差。这可以通过实验方法确定,覆盖大约两个ADC1跃迁区的峰峰值扰动噪声对DNL的改善最佳。更高的噪声量不会明显改善DNL.两个ADC1跃迁区覆盖1024 LSB峰峰值,或者大约155 LSB rms(峰峰值高斯噪声除以6.6即得到均方根值)。

图9中的第一幅图显示一小部分输入信号范围内的无扰动DNL.水平轴经过放大,以显示两个相距68.75 mV (512 LSB)的分级点。第二幅图显示增加155 LSB rms扰动后的DNL,该扰动量相当于大约–20.6 dBm.请注意,DNL得到显着改善。

图9:无扰动和有扰动的AD6645 DNL

扰动噪声可以通过多种方式产生。可以使用噪声二极管,但简单地放大器宽带双极性运放的输入电压噪声是更经济的解决方案,这种方法已在参考文献3、4、5中详细说明,在此恕不赘述。

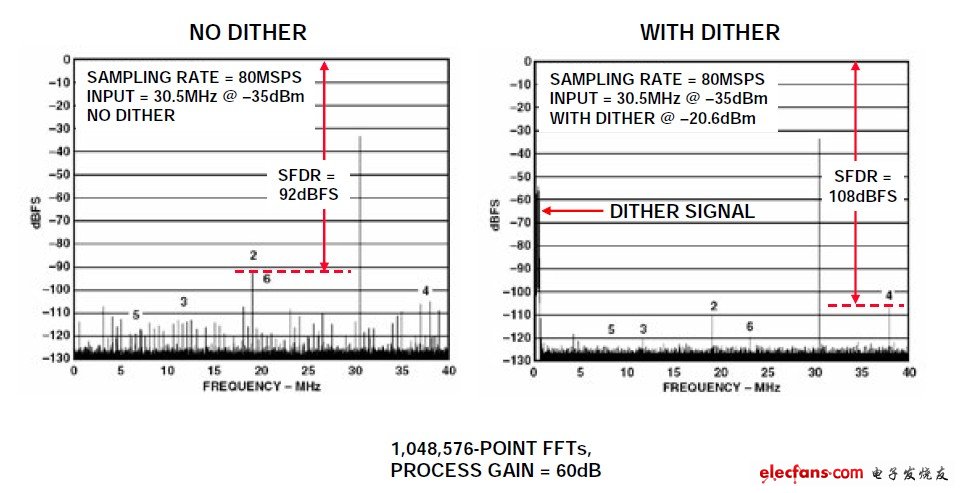

利用带外扰动获得的SFDR大幅改善结果如图10的深(1,048,576点)FFT所示,其中AD6645以80 MSPS的速率对一个–35 dBm、30.5 MHz信号进行采样。请注意,无扰动时SFDR约为92 dBFS,有扰动时约为108 dBFS,提高幅度达16 dB!

图10:无扰动和有扰动的AD6645 FFT图

AD6645 ADC由ADI公司于2000年推出,直到最近,它仍是代表SFDR极致性能的产品。自从推出该器件后,工艺技术和电路设计两方面的进步推动ADC向更高性能发展,例如AD9444(14位、80 MSPS)、AD9445(14位、105/125 MSPS)和AD9446(16位、80/100 MSPS),这些ADC具有非常高的SFDR(对于70 MHz满量程输入信号,典型值大于90 dBc)和低DNL.

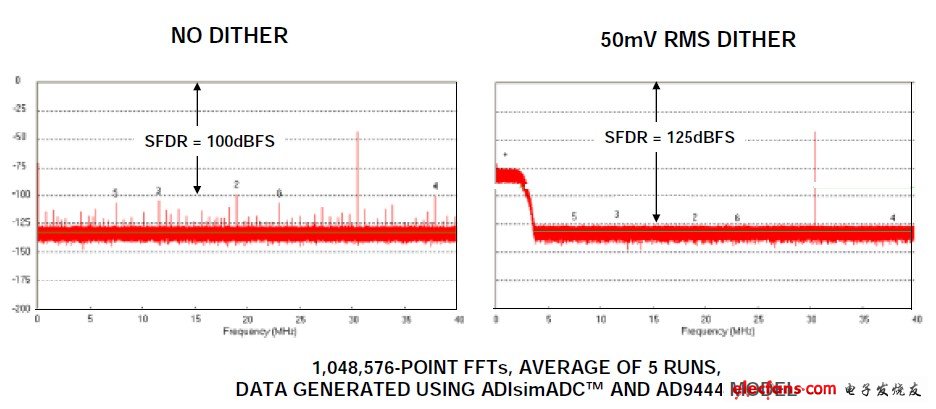

在一定的输入信号条件下,增加适当的带外扰动信号同样可以改善SFDR性能。

图11显示了有扰动和无扰动下的AD9444(14位、80MSPS)FFT.在这些输入条件下,添加扰动使SFDR提高25 dB.所示数据是利用ADIsimADC程序和AD9444模型获得。

图11:14位、80MSPS ADC AD9444,fs = 80MSPS,fin = 30.5MHz,信号幅度 = –40dBFS

虽然图10和图11所示的结果相当惊人,但不应认为,增加带外噪声扰动一定就会改善ADC的SFDR,或者在所有条件下都适用。正如之前提到的,扰动无法改善ADC前端电路的线性度。即使是近乎理想的前端,扰动的效果也将高度依赖于输入信号的幅度和扰动信号本身的幅度。例如,当信号接近ADC的满量程输入范围时,传递函数的积分非线性可能会成为确定SFDR的限制因素,扰动将没有助益。务必认真研究数据手册,某些情况下,其中可能给出了有扰动和无扰动的数据以及幅度和带宽建议。扰动可能是更新一代中频采样ADC的内置特性。

结束语

在本文中,我们说明了所有ADC都有一定量的折合到输入端噪声。在精密、低频测量应用中,以数字方式对ADC输出数据求平均值可以降低该噪声,代价是采样速率会降低并且需要额外的硬件。该均值方法实际上可以提高ADC的分辨率,但无法降低积分非线性误差。