3.3 关键信号与非关键信号

在仿真分析前,先对系统中的信号进行划分,划分为关键信号与非关键信号。划分的原则主要是根据器件驱动沿速率快慢、工作频率的高低与信号线长度等条件进行划分,当然还应依实际的设计而定。

在本系统中,关键信号有:时钟信号;CPU与SDRAM、CPU与FLASH等 存储 器的数据线、地址线以及读写等控制信号线。其中最关键的是SDRAM与 MC9328MX1之间的连接走线,它们的信号完整性好坏直接影响着MC9328MX1能否将数据正确存取于SDRAM 中。

4 仿真分析与结果

4.1 LineSim仿真

在原理图完成之后即可进行布线前信号完整性仿真,在这里使用HyperLynx的布局前分析工具LineSim完成布线前仿真。LineSim用在布线设计以前约束布线和各层的参数、设置时钟的布线拓扑结构、选择元器件的速率、诊断并避免信号完整性、电磁辐射等问题。

LineSim进行布线前仿真是很方便的,将厂商提供的IBIS模型添加到相应的模型库中,在LineSim原理图中将驱动端,接受端以及它们之间的连线方式设置好,就可以进行仿真了。LineSim还提供了对仿真结果一些建议,如连线的拓扑结构、连线的长度、端接电阻和电容的数值是否匹配等。

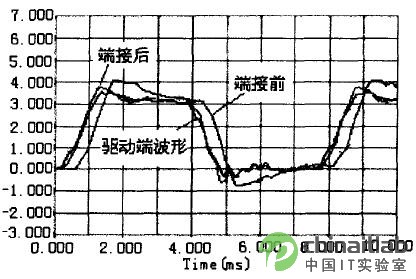

通过在布线之前信号完整性分析对布局进行指导,对逻辑器件的类型进行选择,决定哪些信号需要端接,以及采用何种端接方法及端接电阻的阻值大小。图1是在工作频率为100 MHz时数据线D0添加33欧姆的并联电阻端接前与端接后信号完整性分析的不同结果,可以看出在端接后明显消除了上冲与下冲,且振荡也大幅度地减小了

图1 数据线D0仿真波形

4.2 BoardSim仿真

在布线前信号完整性仿真指导下完成布局布线之后,还可能存在一些信号完整性问题,如相邻线网之间的串扰、EMC等,所以需要进行布线后的信号完整性仿真,对完成布线后的设计进行进一步的分析。在这里使用HyperLynx的布局后分析工具BoardSim完成信号完整性分析。BoardSim用于布线以后快速地分析设计中的信号完整性、电磁兼容性和串扰问题,生成串扰强度报告,区分并解决串扰问题。

对于某一网络,像LineSim一样,BoardSim可以进行单独仿真,BoardSim还可以进行串扰仿真,相互耦合干扰的网络仿真结束后显示为白色。通过进行串扰仿真,可以很方便的找出相互干扰的网络,通过改变网络的间距或者是减小介质层厚度可以减小串扰。