3.1 OV7670的结构及其工作原理

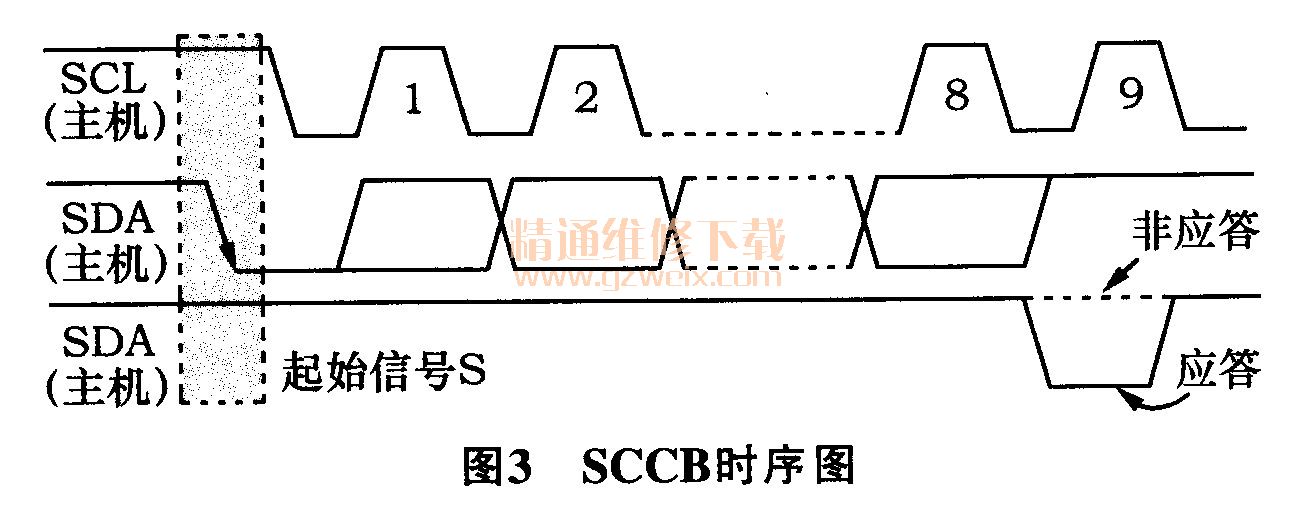

OV7670摄像头是整个系统的最前端,其集成了一个640x480的感光阵列、帧(行)控制电路、视频时序产生电路、模拟信号处理电路、A/D转换电路、数字信号输出电路及寄存器SCCB编程接口。感光阵列得到原始的彩色图像信号后,模拟处理电路完成诸如颜色分离与均衡、增益控制、gamma校正、白电平调整等主要的信号处理工作,最后可根据需要输出多种标准的视频信号。视频时序产生电路用于产生行同步、场同步、混合视频同步等多种同步信号和像素时钟等多种内部时钟信号,外部控制器可通过SCCB总线接口设置或读取OV7670的工作状态、工作方式以及数据的输出格式等,其SCCB控制时序如图3所示。

其中,SCL为由主机发出的单向信号线,输出时钟信号,总线空闲时主机驱动SCL为1,当总线挂起时主机驱动SCL为0; SDA为双向数据传输线,既可以由主机驱动也可以由从机驱动。当总线空闲时保持浮动,状态不固定(0, 1或三态高阻)。当总线挂起时,驱动SDA为0。为了不让该总线产生未知的状态,主机和从机必须保持SDA的电平。

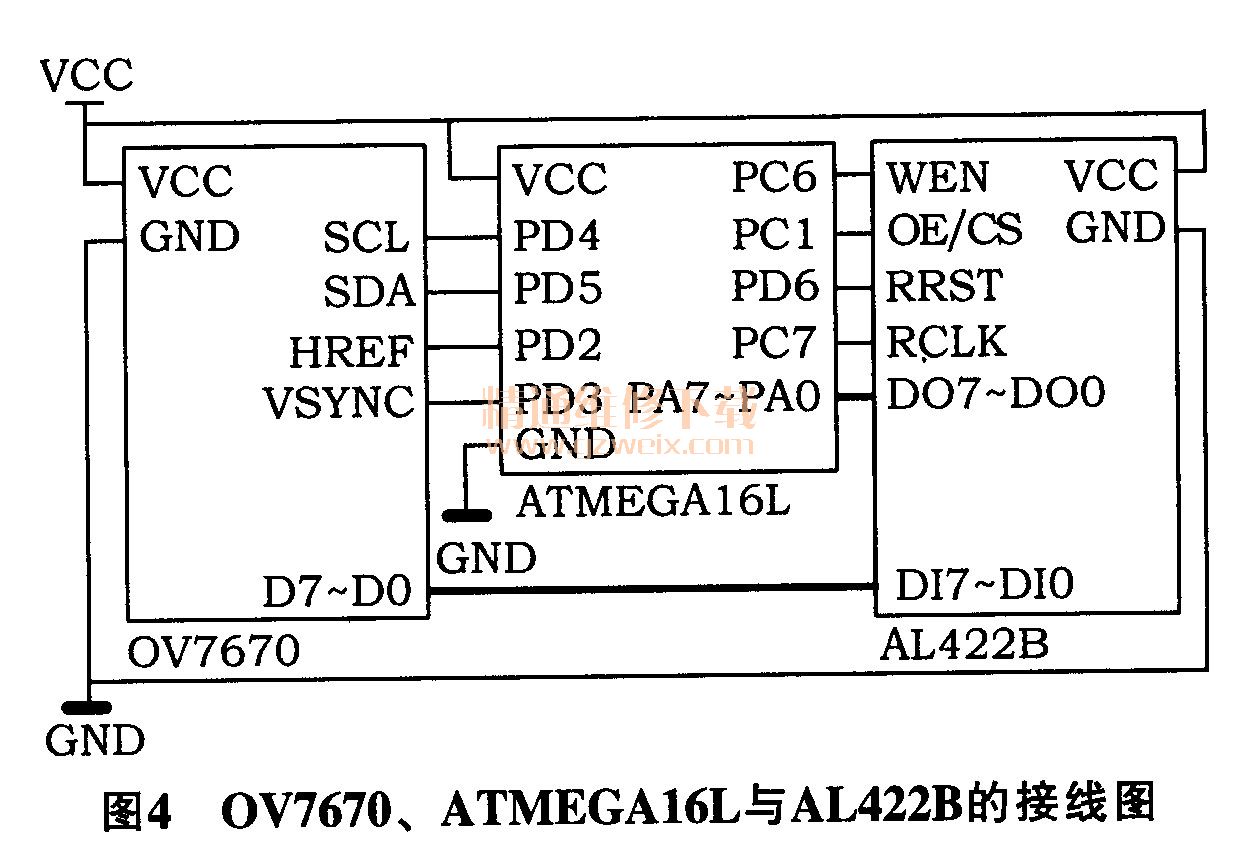

图4为OV7670, ATMEGA16L与AL422B的接线图,HREF为行同步信号,VSYNC为场同步信号,SCL与SDA分别是SCCB总线的时钟线与数据线。其中VSYNC为场同步信号,其下降沿表示一帧图像的开始,HREF为行同步信号,高电平时表示一行的图像数据开始输出。一帧图像开始后,仅当HREF为高,PCLK上升沿时,数据为有效的像素值。对图像数据的采集是通过中断触发的,这里用VSYNC, HREF, PCLK的上升沿触发3个中断。当采集到VSYNC中断时开始一帧图像数据的采集,HREF中断到来时开始采集一行图像数据,一行数据采集完成后,等待下次HREF中断,开始采集下一行数据,以此类推。对HREF中断采集480次,就得到640x480像素点的一帧图像的数据。

3.2图像缓存

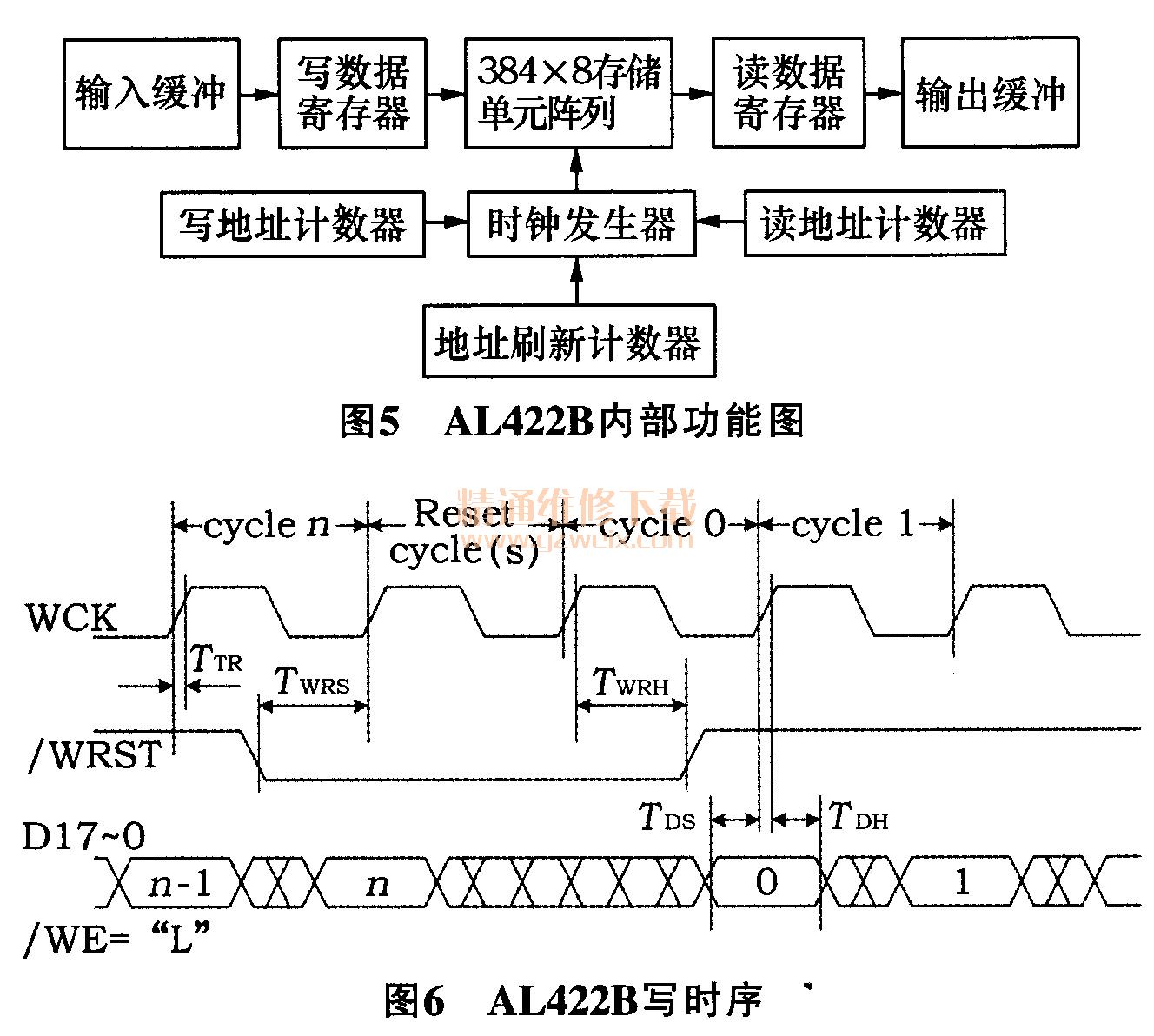

由于OV7670产生的数据在速率上与接口电路不匹配,·因此数据缓存必不可少。AL422B是Aver-Logic公司推出的一个存储容量为393216字节x8位的FIFO存储芯片。由于其所有的寻址、刷新等操作都由集成在芯片内部的控制系统完成,因而使用非常简单。目前市场上的FIFO存储体的存储容量都较小,很难适应视频技术的高速发展,而AL422B的存储空间为3M位,对于普通的视频应用绰绰有余,并且它加快了存取速度,因此可以在本系统中应用。AL422B的内部功能如图5所示。

AL422B的写时序如图6所示。WCK为AL422B的写人时钟,周期最大为1000 ns,最小为20 ns,其上升沿时数据写人,随着该时钟输人,其内部写指针自动增加。显然,AL422B的速度足够。