2.2 采样开关的设计

2.2.1 开关类型的选取

在采样保持电路中,开关的性能对电路有着非常重要的影响。因此对于图1中的开关作了详细设计。在电路设计时,考虑到性能和功耗的优化,在对性能没有明显影响时,尽可能采用简单电路,否则以性能为主。图1中SW2和SW3处的开关主要用于连接到共模参考电压,短接输入端,短接输出端,对其性能要求不是很高,故采用简单的NMOS开关和CMOS互补型开关。在SWl处由于采样开关线性度对电路采样相的线性性能影响最大,如果用一个简单的NMOS开关,当输入信号电压变化时,其导通电阻也随之变化,这在实际工作中会引起较大的误差。而CMOS开关其导通电阻虽有所减小,但随输入信号的变化,其栅-源电压会随之改变,因此信号仍有失真,所以本文采用了一种线性度更好的栅压自举开关。

2.2.2 开关参数设计

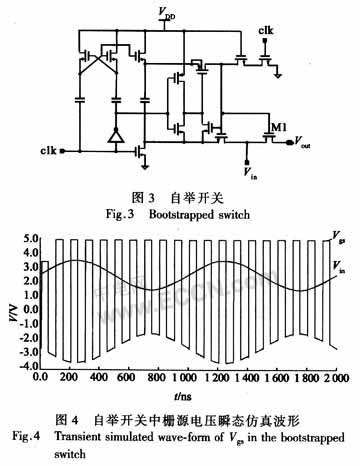

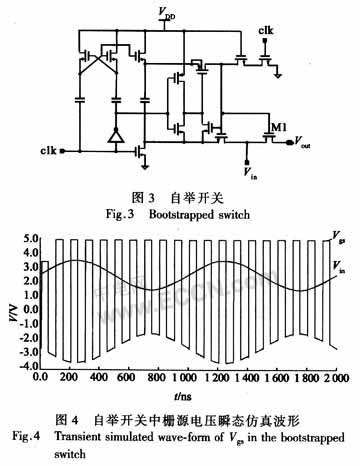

由于小尺寸的开关会带来大的导通电阻,严重影响电路的速度,而大尺寸的开关则会引入非常大的馈通电容,对前级造成明显的影响。在本电路中,NMOS开关的W/L为12/1时仿真性能最好;对于CMOS互补型开关,其导通电阻的线性度受p管和n管的宽长比比例影响。所以要对管子的宽长比进行优化。经过仿真发现,在本电路中,当PMOS和NMOS的宽度比为2.8/1时,导通电阻Ron在整个工作范围内变化最小,线性度最好。栅压自举开关的电路结构如图3所示。它由时钟倍增电路、传输管和栅-源电压控制电路组成。由于传输管M1的栅-源电压V

gs恒定为V

DD,因此自举开关的导通电阻R

on较小,且基本恒定,线性度较好。图4为输入正弦信号时,开关传输管M

1的V

gs仿真波形,从图中可以看出,其V

gs基本不变,由于受M

1栅上的寄生电容的影响,栅源电压略小于V

DD。

3 运算放大器(OTA)的设计

OTA是采样保持电路的核心,它决定了该采样保持电路的精度和建立时间。由于该采样保持电路运用于12 bit 20 MHz流水线ADC,则要求该放大器的输出在25 ns的建立时间内稳定在最终值0.012%。如果将OTA设为单极点放大器,则可估算出OTA的直流增益最好能达到84 dB以上,单位增益带宽必须大于72 MHz。为了能达到较好的性能,一般都留有一定的余量,因此实际上设计中要比这些值大很多。考虑到普通一级运放的增益不够高;两级运放则速度上又达不到,故本文采用增益增强的折叠式共源共栅运放。

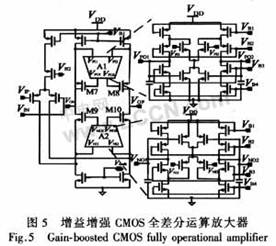

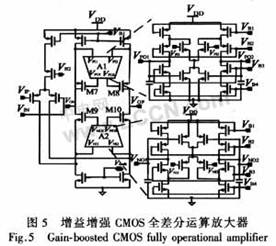

本文采用的放大器为如图5所示的带有A1和A2两个辅助放大器的增益增强型折叠式共源共栅放大器。从工程设计角度考虑,采用统一模块化可简化设计过程,减少设计出错的可能性。因此辅助放大器也采用折叠式共源共栅结构,所有偏置电压都由一个偏置电路产生,并取偏置电流为主运放的1/10,以减小功耗。其中,Al以NMOS管作为输入端,A2以PMOS管作为输入端。考虑到这两个运放的直流输出是为主运放的M7,M8,M9,M10提供直流偏置,不需要大范围的波动,因此采用一种简单实用的共模反馈。另外,辅助放大器的单位增益带宽至少与主放大器的带宽相等,稍大则稳定时间会更短一些,因此可在其输出端接电容来调节带宽,将其控制在主运放第二极点内的合适位置。主运放则采用连续时间型共模反馈。

上一页 [1] [2] [3]