2 LVDS在某成像光电跟踪产品中的应用

2.1 系统应用简介

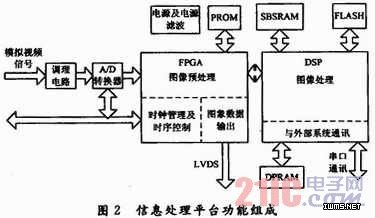

某成像光电跟踪产品信息处理平台采用FPGA+DSP的设计框架,结构框图如图2所示。

该信息处理平台在FPGA和DSP外围增加调理电路、A/D装换器、PROM、SBSRAM、DPRAM、FLASH、电源及电源滤波电路等。FPGA+DSP架构最大的特点是结构灵活,适于模块化设计,能有效地提高算法效率,因而非常适用于成像系统的信息处理。从图2可以看出,该系统通过FPGA,利用LVDS标准电路设计完成图像数据的输出。在该系统中,LVDS有三路差分输出,其中两路传送数据(DA,DB),一路传送时钟(C)。传送格式的要求如下:DA(DAX)为发送16位数据线,传送系统给图像采集设备的所有数据。包括每帧开头发送一个帧计数,帧正程发送图像数据(实时图像数据、滤波图像数据及二值像数据,按DSP要求传送)。图像数据为12位或14位,按需要传送。16位数据的分配如下:最高位为奇偶校验位,“1”表示奇数,“0”表示偶数;次高位为正逆扫信号,“1”表示正扫,“0”表示逆扫;在每帧的开头,图像数据输出之前,添加2个验证字——FDB18540,作为接收方判断每帧数据传送的起始点;帧正程开始后,传图像数据14位,如传的是12位图像数,则其14,13位填0,后12位为图像数据。

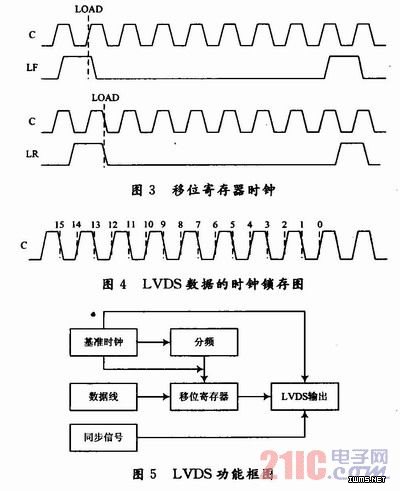

DB(DBX):发送同步信号,每字同步,与首数据最高位同时发出,宽度为半个时钟C(CX):时钟信号,始终保持。在LVDS设计实现过程中参考XAPP233的设计方法,16位数据通过并转串移位寄存器进行移位处理,将偶数位锁存于传送时钟的上升沿,奇数位锁存于传送时钟的下降沿。其输入/输出采用DDR技术,保证双沿触发。移位寄存器时钟示意图如图3所示。最终输出数据的时钟锁存的位置如图4所示。LVDS电路功能框图如图5所示。