2.1 DDR的信号完整性问题

高速总线信号的传输往往需要考虑信号完整性问题。DDR的信号线不是普通的信号线而是传输线,因而传输线上的过孔,或者连接器等不连续阻抗因素都会影响接收端的信号完整性。主要有过冲和下冲、振铃及串扰等影响,交流噪声以及直流电压的一些不准确因素也同样影响信号传输的性能。

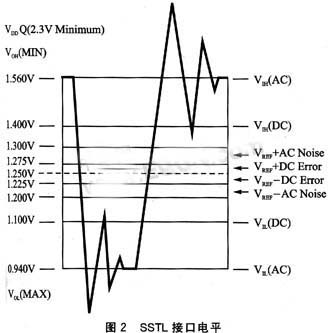

DDR为了实现更高的信号频率,SSTL高增益差分接收器的接收电平往往是偏置在参考电平(VREF)附近,使用这样的接收器允许更小的电压摆幅、更少的信号反射、更低的电磁干扰和更短的建立时间,比LVTTL能适应更高的时钟频率。图2所示的是SSTL接口电平。交流逻辑电平是在接收器端的接收电平,在接收器处交流逻辑参数(包括建立和保持时间)都必须最佳,而直流逻辑电平则提供一个滞后的接收电平点。当输入电平穿过DC直流参考点时,接收器转变到新的逻辑电平并且保持这个新的状态,只要信号不低于门限电平。因此,SSTL总线不易于受过冲、下冲和振铃的影响。

2.2 基于布线考虑的DDR信号分组

DDR控制器包括超过130个信号,并且提供直接的信号接口连接内存子系统。这些信号根据信号的种类可以分为不同的信号组,如表1所列。

其中,数据组的分组应该以每个字节通道来划分,DM0、DQS0以及DQ0~DQ7为第1字节通道,DM1、DQS1以及DQ8~DQ15为第2字节通道,以此类推。每个字节通道内有严格的长度匹配关系。其他信号走线长度应按照组为单位来进行匹配,每组内信号长度差应该严格控制在一定范围内。不同组的信号间虽然不像组内信号那样要求严格,但不同组长度差同样也有一定要求。具体布线要求见2.4小节。