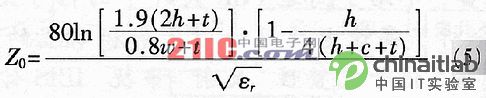

式中,Z0是微带线的特性阻抗(Ω),w是印制导线宽度(英寸),t是印制导线存度(英寸),h是电介质厚度(英寸),c是印制导线之间的距离,εr是印制电路板电介质的相对介电常数。

2.2 反射引起的问题及解决方法

由于存在传输线效应,从反射的角度来看,会出现以下信号完整性问题:

(1) 信号反射形成信号振荡。反射回来的信号会在源端和终端之间形成多次反射,加上传输线效应引起的过大的电感和电容,会导致信号振荡,即在一个逻辑电平附近上下震荡。这种现象尤其会出现在周期性的时钟信号上,从而导致系统失败。

(2) 信号反射会形成信号过冲和下冲。虽然一般来说每个信号的输入端都具有保护作用的齐纳二极管,但过程电平有效会远远超过元件电源电压范围,损坏元器件。

(3) 多次跨越逻辑电平门限。信号在跳变的过程中可能多次跨越逻辑电平门限,它是信号振荡的一种特殊的形式,即信号的振荡发生在逻辑电平门限附近,多次跨越逻辑电平门限会导致逻辑功能紊乱。

解决反射的根本办法是使信号具有良好的终端匹配,控制传输线的长度。同时也可利用IBIS仿真对系统信号进行优化。

3 串扰

3.1 串扰的形成和计算

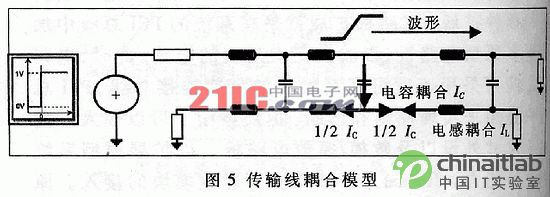

在高速信号系统设计中,反射属于单信号线现象,当然包括地平面问题。但串扰不同,它是两条信号线之间以及地平面之间的耦合,所以又称为三线系统。形成串扰的根本原因是信号变化引起周边的电磁场发生变化,特别是对于高速信号,信号的上升和下降沿的时间可以达到ps级,高频分量非常丰富,信号线之间的寄生电容和电感容易成为串扰信号的耦合通道。下面以图5所示的传输线耦合模型为例进行分析。传输线上分布着电感分量和电容分量,所以整个信号之间的串扰由两部分组成,即容性耦合干扰和感性耦合干扰。容性耦合干扰是由于干扰源(Aggressor)上的电压变化在被干扰对象(VICtim)上引起感应电流从而导致的电磁干扰,而感性耦合干扰则是由于干扰源上的电流变化产生的磁场在被干扰对象上引起感应电压从而导致的电磁干扰。感性串扰和容性串扰的基本分析公式如下:

Xtalk(ind)=(Lm)/(Ra×Tr) (6)

式中,Lm是互感,Ra是干扰源的终端匹配电阻,Tr是信号上升沿的时间。

Xtalk(cap)=(Ra×Cm)/Tr (7)

式中,Cm是耦合电容,Ra是被干扰对象的终端匹配电阻,Tr是信号上升沿的时间。

3.2 影响因素

从上面的公式可以看出,串扰的大小与很多因素有关,如信号的速率、信号的上升沿和下降沿的速率、PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式等。

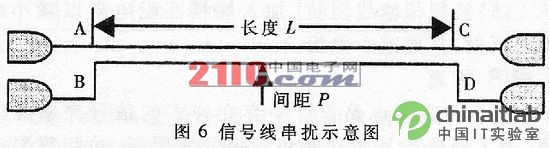

3.2.1 串扰线平行长度和间距对串扰的影响

印制电路板基材与两面的印制导线可看作一个电容器,其电容C可用平板电容器的计算公式来粗略地计算。

C=0.886εr(A/b)(pF) (8)