式中,A是两面导线重叠的面积(mm2),b是层压板电介质厚度(mm),εr是压板的相对介电常数。

当串扰信号线之间的平行长度增加时,将增加两传输线之间重叠的面积,所以线之间的耦合电容也会增加,从而增大电流串扰。同理,当传输线之间的间距减少时,两个耦合的传输线之间的耦合电容也会增加,从而增加串扰的数值。在高速电路设计中,重要的是减少串扰的数值,这样就要从结构上减小平行的长度,而且线间的间距也不能太小。

3.2.2 信号频率和沿速率对串扰的影响

在串扰效应中,除了信号本身的传输频率外,影响很大的还有信号上升时间和下降时间。在现代设计中,经常会出现几百兆赫兹的时钟信号和数字信号,这样信号的上升沿可以达到ps级。在这种情况下,信号的上升时间和下降时间对串扰的影响是不可忽视的。

假设存在一个如图6所示的串扰模型。其中,两线的线宽均为w,两线的线间距为P,而两线的平行长度为L,如不特殊说明,w、P和L的取值分别为w=5mils,P=5mils,L=1.3inches,两线均为顶层微带传输线。PCB板的电介质电常数εr为4.5。分别在不同的频率和沿速率情况下对它进行仿真。干扰源信号的频率不同时。

在同样干扰信号频率(f=20MHz)下,不同干扰源沿速率所产生的信号串扰情况如图7所示。图中标记“1”和标记“2”箭头分别指被干扰对象的远端和近端串扰波形。

3.3 解决方法

从上面的分析来看,在高速电路设计中,除了信号频率对串扰有较大影响外,信号的边沿变化(上升沿和下降沿)对串扰的影响更大,边沿变化越快,串扰越大。所以解决串扰的方法主要从减少干扰源强度和切断干扰路径两个方面进行,有以下几个方法:

(1) 串扰与信号频率成正比,而且在数字电路中,信号的边沿变化(上升沿和下降沿)对串扰的影响最大,边沿变化越快变频分量越丰富,串扰越大,所以尽量少地使用dV/dt高的信号,在超高速设计中可以使用低电压差分信号或其它差分信号。

(2) 在布线空间允许的条件下,在串扰较严重的两条线之间插入一条地线或地平面, 可以起到了隔离的作用,从而减小串扰。

(3) 加大线间距,减小线的平行长度,必须时可以以jog(凹凸)方式走线。

(4) 对于信号速率比较高的信号,可以将它走线经过的微带线和带状线控制在地平面8mil距离内,这样可以显著减少串扰。

(5) 控制传输线阻抗,加入端接匹配电阻以减小或消除反射,从而减小串扰。

4 IBIS仿真

由于在高速电路设计中存在许多的信号完整性问题,为了确保产品的性能和缩短开发周期,迫切需要进行电路的板线仿真。仿真的手段主要有SPICE仿真和I/O Buffer Information Specification(简称IBIS)仿真等。IBIS模型只涉及器件I/O buffer的电气特性,不包含器件内核的结构、工艺和性能等信息,从而有效保护了IC开发商的知识产权,因此与SPICE模型相比,IBIS模型比较容易从器件生产厂家获得;同时IBIS仿真具有很高的精度,而且其仿真速度比SPICE仿真速速快25倍左右。本文只介绍IBIS仿真。

4.1 IBIS模型的组成要素

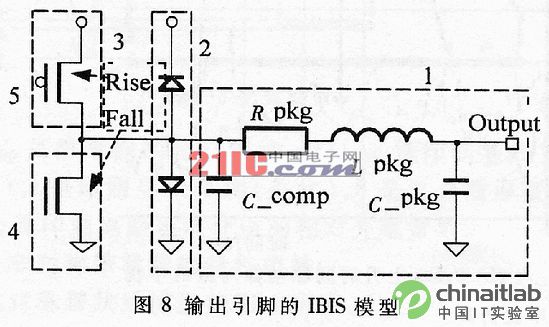

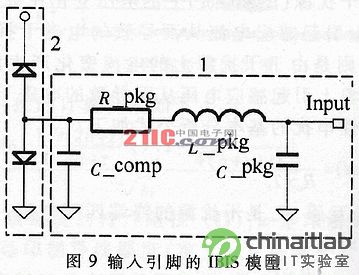

按器件引脚输入、输出性质的不同,IBIS模型中所包含的要素也不同。主要有两种,即输出引脚和输入引脚模型,图8描述的是输出引脚的模型。模块1表示自器件Pad到PIN的寄生参数,其中C_comp表示由输出Pad、钳位二极管引起的输出电容,L_pkg、R_pkg以及C_pkg表示由绑定引线和Pin引起的电感、电阻和电容。模块2表示器件内部的ESD保护二极管或钳位二极管,模块3表示开关管的开关动态特性,在模型文件中用dV/dt表示,决定信号的沿速率。模块4和模块5分别表示下拉开关管和上拉开关管,用模型文件中的V/I曲线表示。图9描述的是输入引脚的IBIS模型,它只包含模块1和模块2。

4.2 IBIS模型仿真步骤

由于IBIS仿真模型不但含有每个引脚的寄生参数,如封装寄生电感、电容和电阻,而且有表示信号沿速率的dV/dt和端口特征的V/I曲线,所以IBIS仿真具有精度高、仿真速度快的特点,被现在的EDA软件广泛采用,如Cadence和Mentor等。下面介绍Cadence软件的仿真步骤:

(1) 从半导体厂家获取IBIS模型。

(2) 进行IBIS模型的校正,这一步非常重要,因为有时候厂家提供的IBIS模型有错误。

(3) 在原理图设计时,将相应的IBIS模型赋予每个器件,然后进行PCB设计。