二、数字板信号流程分析

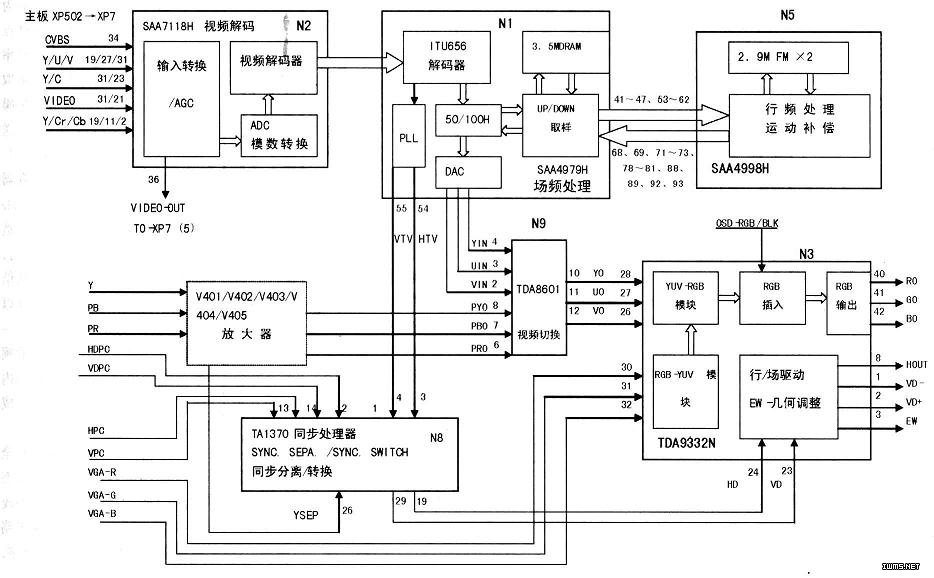

P21机芯在原HiD电视的基础上,将由TDA9332+TDA9143及倍行芯片NV320更换为由飞利浦公司推出的1OOHz变频方案,由SAA7118H进行视频解码,SAA4979H完成50/60Hz转变为100/120Hz的倍频处理,及75Hz加行的四种倍频扫描模式变换,由SAA4998H进行运动补偿,最后由SAA4979H输出YUV信号,送入视频切换开关TDA8601中。经TDA8601切换后的信号送到TDA9332N进行显示处理,其组成框图如上图所示。由上述系列变频芯片组成的数字处理组件,在整体线路上完全不同于原TCLHiD299S.P高洁彩电的变频线路。

(1)数字板信号流程

数字板通过XP1~XP3及XP7、XP8五个插座与外部电路连接。其中,通过XP1的信号是TDA9332N输出的RGB、暗电流(Iom)及由TA1370输出的VM信号、VMSW信号;XP2为VGA的RGB及VGA的行场同步信号输入口;XP3为HDTV信号输入口,输入VPC、HPC、Pr、Pb、Y信号;XP7为与主板上的XP502的接口,输出video信号,并输入行消隐、ABL、Y信号、信号、视频2信号、C信号、Cb信号、Cr信号、Y信号、+5V/+8V电压;XP8为主板上的XP501的接口,输入OSDR/G/B/BLK信号复位信号、9V电压,输出正反场向锯齿波信号、EW信号、行激励信号。

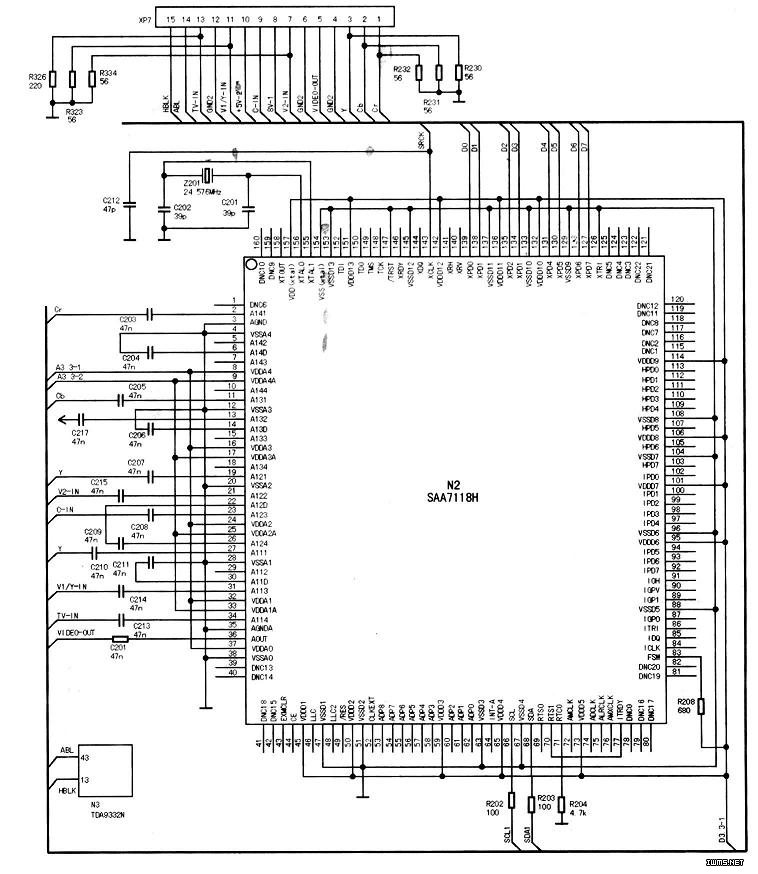

由XP7端口输入隔行视频信号,如下图所示,端口的(1)~(3)脚分别输入隔行色差信号Cr、Cb、Y,分别经电容C203、C205、C207派波后,从N2的(2)、(11)、(19)脚进入,经N2视频解码后从(36)脚输出,由电阻R201限幅后从XP7端口的(5)脚输出。XP7的(7)脚输出的是AV2信号,经电容C215滤波后,从N2(21)脚输入。XP7的(9)脚褓出的是S端子的色度信号,经电容C208波后从N2的(23)脚输入。XP7的(11)脚输出的是AV1的视频信号或者是S端子的亮度信号,经电容C214耦合后,从N2的(31)脚进入。XP7的(13)脚输出的是IV视频信号,经电容C213滤波后,从(34)脚进入。XP7的(14)脚输出的是ADL信号,经C301、R321滤波及R301、R302对8V电压进行分压后,从N3的(43)脚进入,XP7的(15)脚输出行消隐信号,经电阻R313限幅后从N3的(13)脚进入。

所有的隔行视频信号均由XP7的端口进入,由N2进行视频解码。SAA7118H内置输入信号选通开关,支持CVBS、VIDEO、Y/U/V及VIDEO等模拟信号输入。N2先对输入的模拟信号进行处理,再送人ADC模数控制电路,将模拟信号变成数字信号,然后通过4H自适应数字梳状滤波器进行亮、色分离,再将色度信号进行色差分离,生成寸、Cb、Cr信号,最后由N2的(139)、(138)、(135)、(134)、(131)、(130)、(128)、(127)脚输出8bit数字YUV信号。

SAA7118H支持所有彩色制式信号解码。

(155)、(156)脚外接晶振(24.576MHz),与内部电路一起可产生所有彩色制式的基准副载波。

N2受总线控制,其(66)、(68)脚分别是SCL、SDA揣。N2的工作电压是3.3V的直流电压。

(2)变频处理

HiD29208P是一款变频彩电,所有的变频处理都由集成电路 SAA4979H来完成。SAA4979H 主要用于将 50/60Hz信号变成 100/120Hz 信号,并且与 SAA4998H(运动补偿)连接使。 用,实现50/60Hz逐行处理及 75Hz加行处理。

SAA7118H输出 8bit数字 信号,通过N1(SAA4979H)的 ((7)~(14)脚送入内部的解码器 ITU656 中,将YUV信号按照 ITU656 的标准进行 4:2:2取 样,即 Y信号的取样频率为 27MHz,单行有效像索取样点 为 720;色差信号的取样频率 为 13.5MHz,单行有效像素取 样点为 360。4:2:2信号经过噪 声检测及数字降噪处理后,送 入N1 内置3.5M场存储器中。 该场存储器具有 1 个写寄存器 和 2个读寄存器功能,以 50Hz 的频率慢速写入一场信号,然 后以 1OOHz的频率高速读出, 即在20ms时间内读出两场信 号 (本场及存储场)。同样以 15.625kHz的频率慢速写入一 行信号,然后以 31.25kHz的频 率高速读出,即在64μs 时间内 读出两行信号,完成1fh变成 2fh信号的过程。

2fh信号经过Panorama(全景缩放)、DLTI (动态亮度瞬态改善)、DCTI (动态彩色瞬态改 善)等图像处理及图像改善电路 后,送入DAC数模控制电路,变成模拟的YUV信号,从(44)、(46)、(48)脚输出,同时YUV信号需满足Y:U:V=1:1.33:1.05的比例关系。N1(58)、(59)脚外接的12MHz晶振电路提供PLL电路的基准频率,经ITU656鉴频、锁相,并在内置的微处理器控制下产生行、场同步信号HTV、VTV,从N1(54)、(55)脚输出。N1(111)、(112)脚分别是SDA、SCL,脚。N1的供电电压为直流电压3.3V。

从N1扩展口输出的16bit的YUV隔行信号从(41)~(47)、(53)~(62)脚送入SAA4998H(N5),先经过数字动态降噪电路后进人行存储器,分别存入A(奇数场)及B(偶数场)的行数据,然后将A场及B场相邻行信号进行比较、运算,求出运动矢量,将运算结果分别存入内置的A场存储器FM1及B场存储器FM2中,得到新的A1场和B1场信号,再按A、A1、B、B1的场顺序,逐行输出扫描信号。16bitYUV逐行信号经过图像增强(V—PEAKING)处理后,从N5(68)、(69)、(71)~(76)、(78)~(81)、(88)、(89)、(92)、(93)脚输出,再送回至SAA4979H。N5的供电电压为1.8V、3.3v。