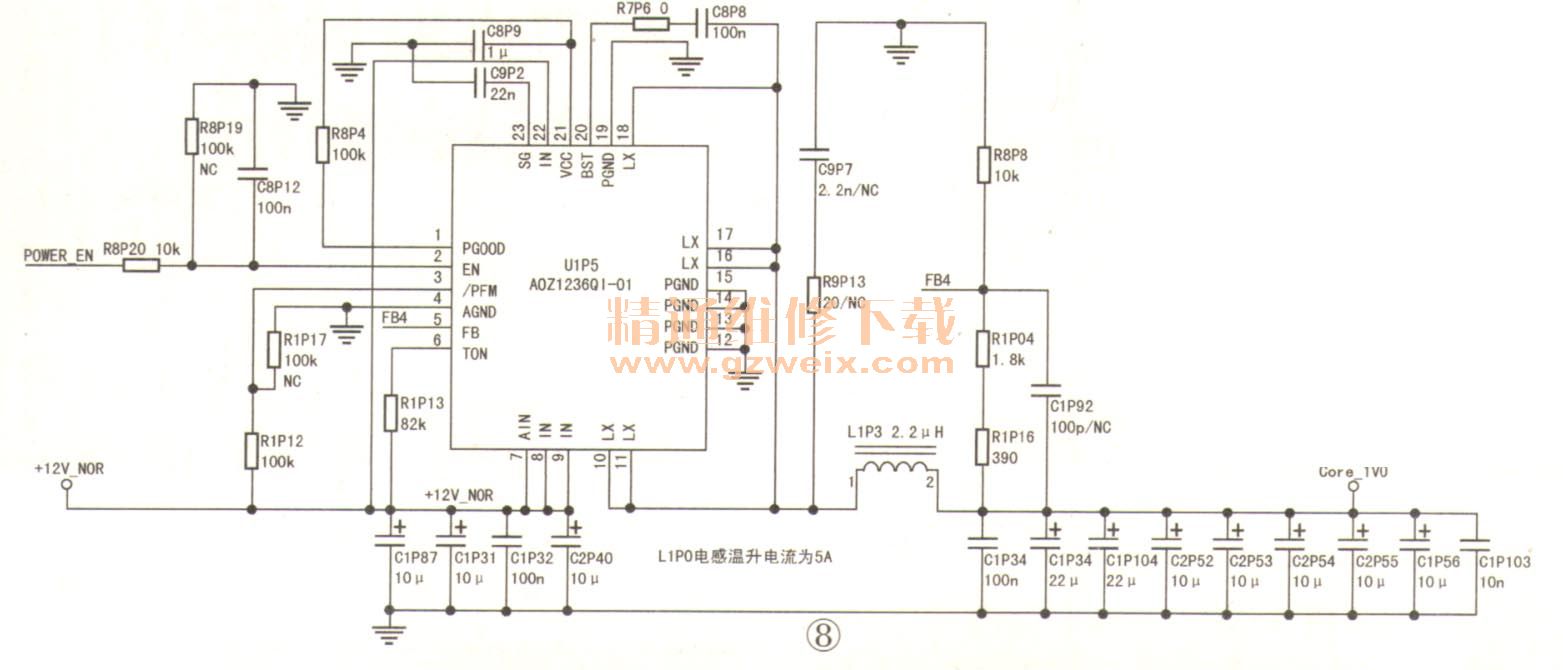

6.CORE供电产生电路(见图8)

开机后,使能信号送到U1P5(AOZ1236QI-01)的②脚,内部电路工作,12V NOR经U1P5变换得到Core_1VO电压,供给主芯片U20内核电路。

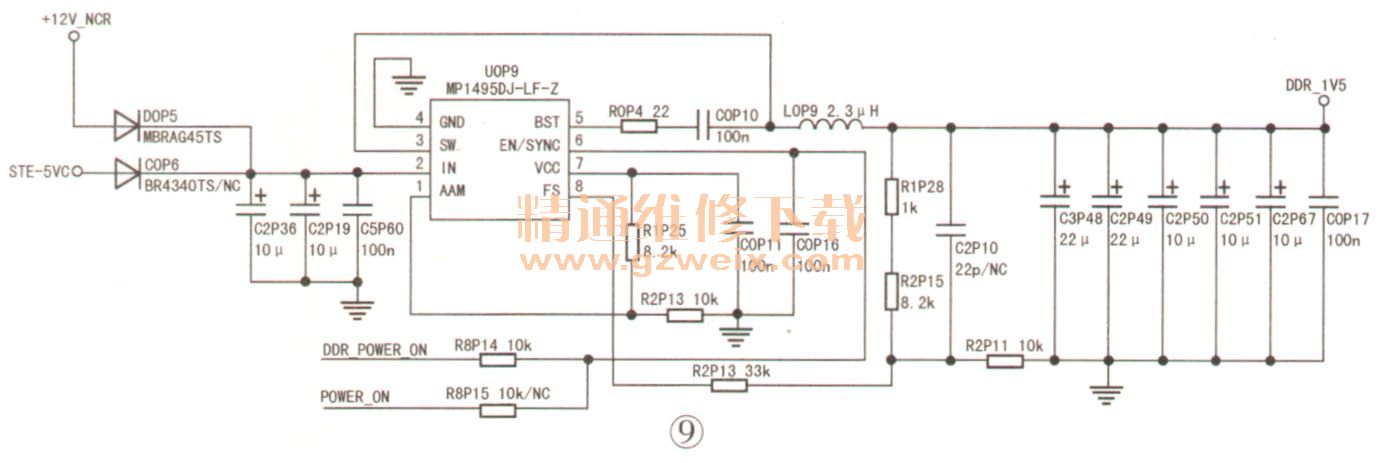

7.DDR_1V5供电产生电路(见图9)

开机后,使能信号送到U0P9 (MP1495DJ-LF-Z)的⑥脚,内部电路工作,12V NOR经U0P9变换得到1.5V电压,供给DDR内核电路。

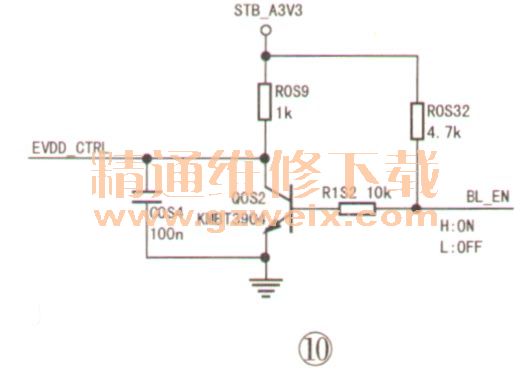

8.背光开/关控制电路(见图10)

U20送来的BL EN信号经Q0S2倒相后,通过插座CNOS 1的①脚送往背光电路,控制背光电路是否工作。

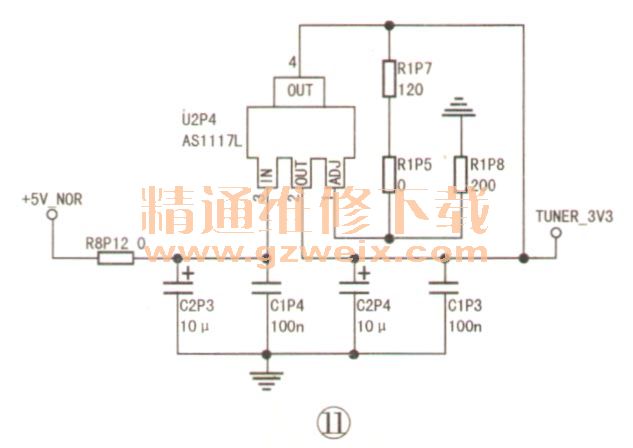

9.TUNER D3V3供电产生电路(见图11)

+ 5V NOR经U2P4稳压后得到TUNER_3V3电压,供给高频头电路。

10.数字音频功放电路(见图12)

该机芯采用丁AS5711+TAS5766双数字音频功放电路,其中,TAS5711(U0A7)为重低音功放IC。U0A7内部集成了数字音频处理、串行音频端口、数字音频接口、串行控制、微控制、SRC、降噪、功放输出、保护逻辑等电路,其②、③、34、35、36、41、44、45脚为24V供电脚,17脚为3.3V模拟供电脚,27脚为3.3V数字供电脚,19脚(PND)是待机控制脚,25脚(RESET)是复位脚,23脚(SDA)、24脚(SCL)为总线数据、时钟脚,15脚( MCLK)为主时钟输入脚,20脚(LRCLK)为串行音频数据左右时钟输入脚,21脚(SCLK)为串行音频数据时钟输入脚,22脚(SDIN)为串行音频数据输入脚,①脚(OUT_A)、46脚(OUT_B)分别为左、右声道音频信号输出脚,36脚(OUT_D) 、39脚(OUT_C)分别为左、右重低音音频信号输出脚,15、20~22脚是12S数字音频信号输入脚。