从(5)式可以看出,V

BE与温度并不是简单的线性关系,最后一项就是非线性项。其中η是与工艺相关的量。如果发射极电流是PTAT电流,那么α=1;如果发射极电流与温度无关,则α=0。图1中流入Q1、Q2的电流是PTAT电流,故有:

因流入Q3的电流也与温度无关,故有:

由于流过R4和R5的电流I

NL正比与V

NL,故可表示为:

设M1、M2、M3和M4管的宽长比一样,所以,流过四个管子的电流相等且都等于:

从式(10)可以看出,式子的第三项用来消除V

EB1的非线性,这样,结合(6)式可得:

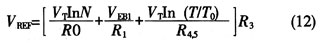

这样,由(10)式可以得到输出的基准电压源为:

2.2 低噪声箝位运放的设计

在基准源中,箝位运放的主要作用是通过电流负反馈使与输入端连接的结点的电压强制相等,并且与电源电压无关。可用运放的输出对电流源进行适当的偏置,使其流过的电流与输入电压无关,从而使R的电流为PTAT电流。实际的运放通常会存在失调电压、有限增益以及运放噪声,这些都会对基准电压源的性能造成影响,由于基准电压源一般工作在低频条件下,因此,对运放的频率特性要求不高。

本文在设计低噪声箝位运放的过程中,重点考虑了以下几个因素:

(1)由于运放的两个输入端基本为固定电位,不需要考虑动态范围,因此,运放的设计不考虑共模输入范围;为了保证电路适用于低电源电压场合,cascode结构不再适合,因此,本文选用普通两级运放的设计方式;

(2)选用PMOS作为运放的输入级。因为PMOS的载流子与空穴的迁移率比NMOS的电子迁移率低2~5倍,故可以较大的减小1/f噪声。同时由于1/噪声与MOS管的面积成反比,因此,输入管的面积需要做的很大;

(3)为了使1/f噪声最小化,负载晶体管的栅长应该比输入管的栅长更长;

(4)减小箝位运放的带宽可以有效的减小热噪声的影响。

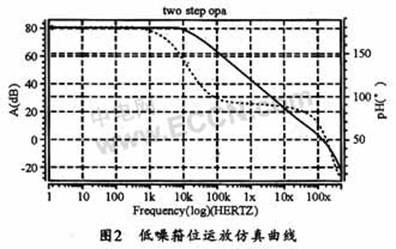

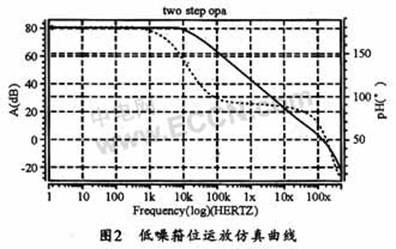

经过仿真可以得到如图2所示的低噪声箝位运放的频率特性曲线,该曲线表明箝位运放的开环增益为81dB,单位增益带宽为139 MHz,相位裕度为61°,失调电压为0.02 mV,可见该运放能够满足系统要求。

上一页 [1] [2] [3]