2 基带处理器电路

在iPhone 5手机中,基带处理器完成率射频信号的解调处理,基带处理器使用了单独的电源管理芯片为其供电。

2.1 基带处理器简介

iPhone 5手机基带处理器使用了MDM9615,MDM9615是美国高通推出的支持LTE(FDD和TDD)、双载波HSPA+、EV-DO版本B和TD-SCDMA的Mobile Data Modem(MDM)芯片,该芯片组将采用28nm节点技术制造,是MDM9600产品系列高度优化的后继产品。该芯片组在调制解调器性能、功耗、主板及BOM费用方面均有改善。

新的芯片组配备一个专用处理器,从而使OEM厂商凭借附加的增值服务令其产品实现差异化,无需外部应用处理器就能开发WiFi热点产品。两款芯片均兼容高通公司的Power Optimized Envelope Tracking(Q-POET)解决方案。该解决方案能够提供更好的功耗和散热能力,从而实现更小的终端外形。

芯片组还通过使用高通公司的干扰消除与均衡(Q-ICE)算法实现业内领先的调制解调器性能,从而使用户

数据流量更高,网络容量更大。除支持LTE TDD外,MSM9615还支持TD-SCDMA,这使其成为一种非常适合中国移动宽带市场的优化的芯片组解决方案。

MDM9615和MDM8215可与WTR1605射频IC和PM8018电源管理芯片配对,提供高度集成的芯片组解决方案,这是一款支持4G的基带处理器。

基带处理器电路框图如图6所示。

2.2 存储器电路

2.2 存储器电路

基带处理器MDM9615使用了MX25U1635E型号(U601 RF)存储器,存储器和基带处理器之间的通信使用了SPI接口。

1. SPI接口

SPI(Serial Peripheral Interface,串行外设接口),它可以使MCU与各种外围设备以串行方式进行通信以交换信息。SPI有三个寄存器,分别为控制寄存器SPCR,状态寄存器SPSR,数据寄存器SPDR。

外围设备包括FLASH、RAM、网络控制器、LCD显示驱动器、A/D转换器和MCU等。SPI

总线系统可直接与各个厂家生产的多种标准外围器件直接接口中,该接口一般使用4条线:串行时钟线(SCLK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线NSS(有的SPI接口芯片带有中断信号线INT、有的SPI接口芯片没有主机输出/从机输入数据线MOSI)。

SPI接口的全称是Serial Peripheral Interface,意为串行外围接口,是Motorola首先在其MC68HCXX系列处理器上定义的。SPI接口主要应用在_PROM、FLASH、实时时钟、AD转换器,还有数字信号处理器和数字信号解码器之间。

SPI接口是在CPU和外围低速器件之间进行同步串行数据传输,在主器件的移位脉冲下,数据按位传输,高位在前,低位在后,为全双工通信,数据传输速度总体来说比PC总线要快。

接口包括以下4种信号。

(1)MOSI:主器件数据输出,从器件数据输入;

(2)MISO:主器件数据输入,从器件数据输出:

(3)SCLK:时钟信号,由主器件产生;

(4)NSS-从器件使能信号,由主器件控制,有的IC会标注为CS(Chip select)。

在点对点的通信中,SPI接口不需要进行寻址操作,且为全双工通信,显得简单高效。多个从器件硬件连接示意图如图7所示。

在多个从器件的系统中,每个从器件需要独立的使能信号,硬件上比I2C系统要稍微复杂一些。

SPI接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后,在SCLK的下降沿上数据改变,同时一位数据被存入移位寄存器。

2. 存储器电路

(1)存储器电路原理图

供电电压PP SMPS3 MSME_ 1.8送到基带处理器存储器U601 RF的B2、C2、D3脚,U601 RF通 SPI总线与基带处理器MDM9615进行通信。

基带处理器MDM9615的存储器电路如图8所示。

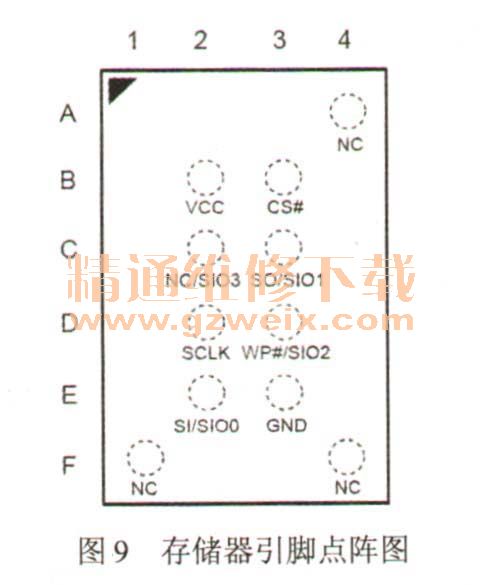

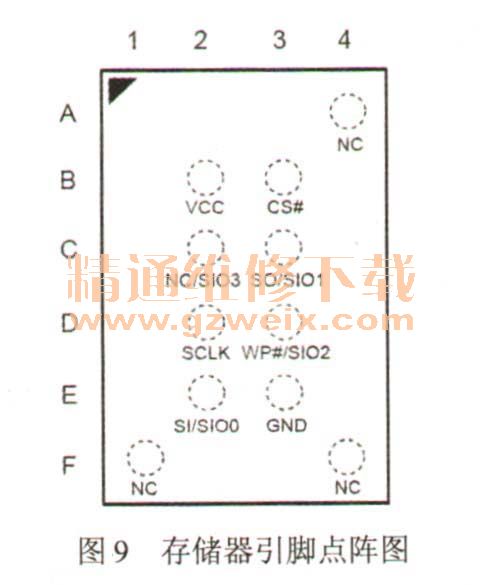

(2)存储器引脚点阵图

存储器引脚点阵图如图9所示。

2.3 基带处理器接口电路

2.3 基带处理器接口电路

1. 时钟

(1)19.2MHz晶体振荡器信号

19.2MHz晶体振荡器信号由基带电源管理芯片PM8018输出送至基带处理器MDM9615的V20、B12脚。

19.2MHz晶体振荡器信号电路如图10所示。

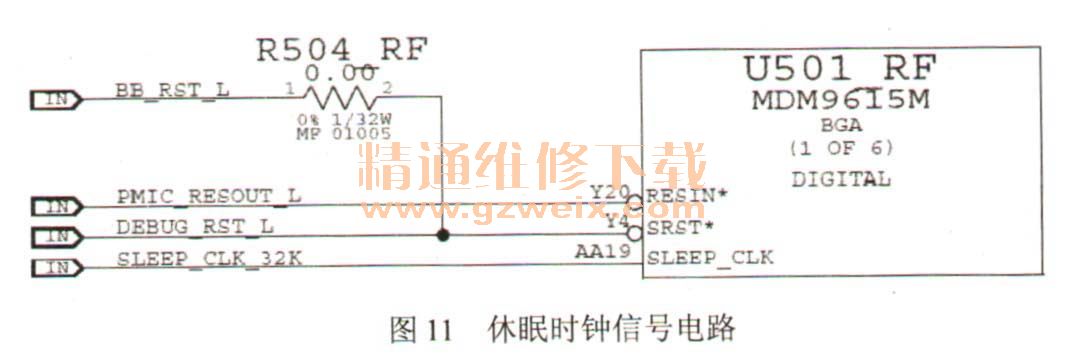

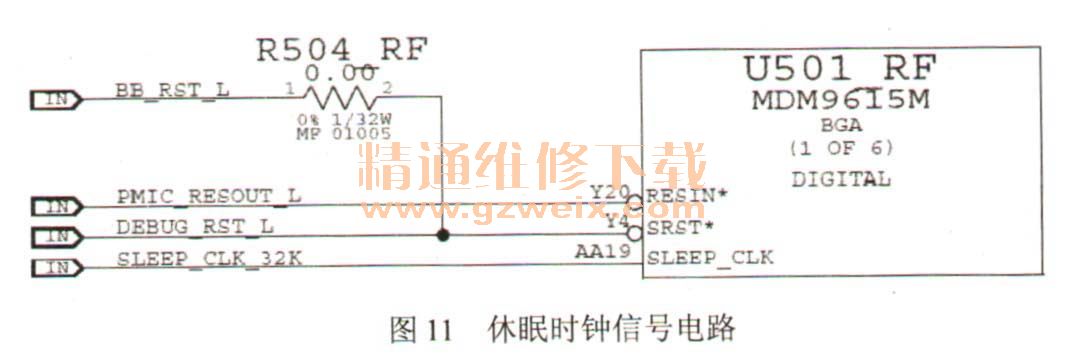

(2)休眠时钟Sleep clock

休眠时钟信号SLEEP CLK 32K由基带电源管理芯片输出,送至MDM9615的AA19脚,如图11所示。

2.模拟基带信号接口电路

基带处理器MDM9615M完成了射频接收基带信号、GPS接收基带信号的解调,完成了射频发射基带信号的调制,如图12所示。

3. HSIC接口

HSIC(High-Speed Inter-Chip,高速芯片间连接)是一种芯片间互连标准,在iPhone 5手机中,基带处理器U501 RF通过HSIC接口与应用处理器U1进行通信,HSIC接口如图13所示。

HSIC接口信号使用四踪数字示波器测量,结果如图14所示。

基带处理器MDM9615M电路还有其他接口电路,不再一一进行介绍,具体可参考整机电路原理图。

3 基带处理器电源电路

基带处理器电源电路完成了基带处理器电路的供电工作,基带处理器MDM9615(U501)供电部分工作时序是决定基带处理器是否工作的关键问题。所以在电源电路中,上电时序非常关键。

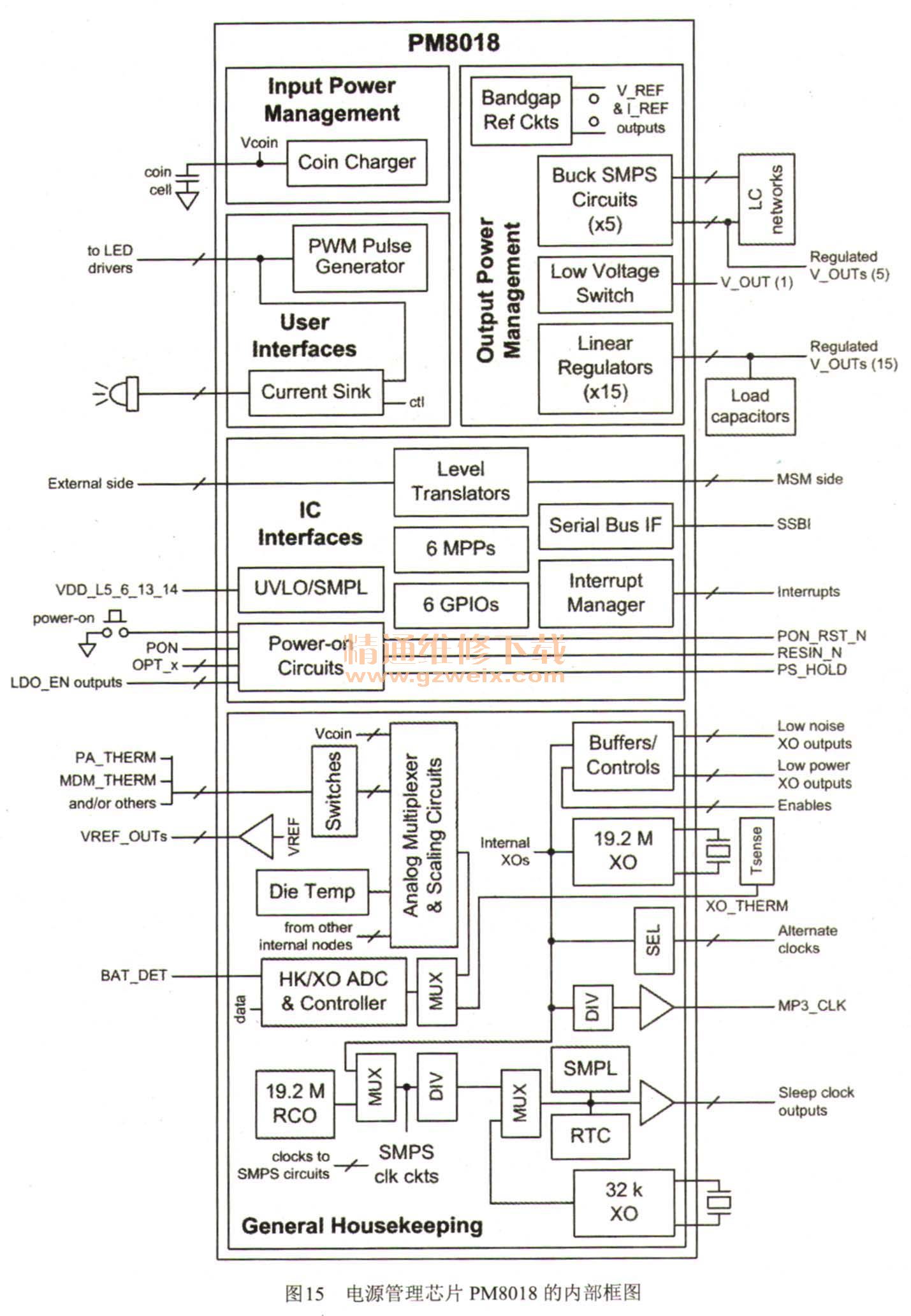

3.1 基带处理器电源芯片简介

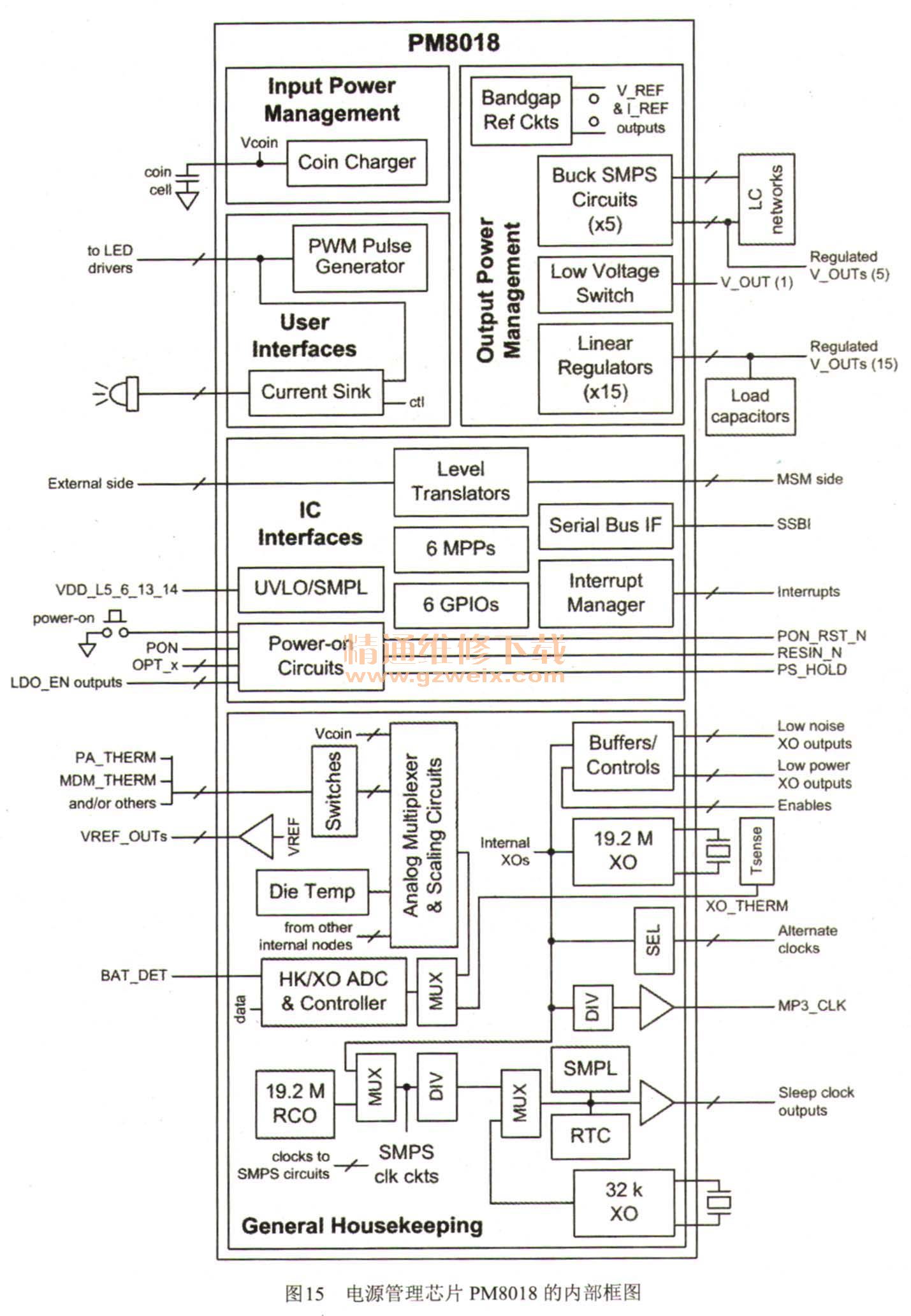

iPhone 5手机的基带处理器电源电路的工作由电源管理芯片PM8018完成,电源管理芯片PM8018内部框图如图15所示。

3.2 上电时序

3.2 上电时序

所谓上电时序是指按一定的顺序给处理器提供供电,保证处理器能够按照顺序启动相应的电路。

基带处理器供电上电时序图如图16所示。

各路信号的先后顺序如下:

(1)RADIO_ON_L(来自AP);

(2)PP_SMPS5_DSP_1V05;

(3)PP_LDO9_PLL_1V05;

(4)PP_SMPS1_MSMC_1V05;

(5)PP_LDO12_MDSP_SW_1V05;

(6)VDDPX_BIAS;

(7)PP_SMPS3_MSME_1V8,PP_LDO2_XO_HS_1V8,PP_LDO6_RUIM_1V8(VDD P1);

(8)PP LDO8_VDDPX_1V2,PP LDO13 VDDPX 2V95,PP_LDO13_VDDPX_2V95,PP LDO4 _VDDA_3V;

(9)PP_LDO5_GPS_LNA_2V5,PP_LDO8_VDDPX_1V2,PP_LDO4_VDDA_ 3V3;

(10)VREG _XO;

(11)Sleep_CLK;

(12)XO _OUT_ D0;

(13)PON _RESET _N(电源输出复位信号到基带处理器);

(14)PS_ HOLD(来自基带处理器)。

储存器供电和锁相环供电第一个启动,然后数字电路核心供电才启动工作,以便内部电路I/O部分电路工作。启动数字I/O电路以后,SSBI申行总线对射频和PM8018电路进行初始化。

以上电压工作的先后顺序是,当第一个电压达到90%之前,下一个电压开始产生,也可能是下一个电压是由上一个电压产生的。

以上是基带处理器的开机时序,关机时序正好与之相反。

上一页 [1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] 下一页